# The Application of Tomasulo's Method

Shonagh Hurley B.A. (Mod.) Computer Science Final Year Project 2005 Supervisor: Michael Manzke

# THE APPLICATION OF TOMASULO'S METHOD

by

Shonagh Hurley

## FINAL YEAR PROJECT<sup>1</sup> SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF B.A. (MOD.) COMPUTER SCIENCE AT UNIVERSITY OF DUBLIN, TRINITY COLLEGE DUBLIN, IRELAND 5TH MAY 2005

© Copyright by Shonagh Hurley, 2005

<sup>&</sup>lt;sup>1</sup>This document has been fully typeset in  $L^{AT}EX$

# UNIVERSITY OF DUBLIN, TRINITY COLLEGE DEPARTMENT OF COMPUTER SCIENCE

The undersigned hereby certify that they have read and recommend to the Department of Computer Science for acceptance a thesis entitled "The Application of Tomasulo's Method" by Shonagh Hurley in partial fulfilment of the requirements for the degree of B.A. (Mod.) Computer Science.

Dated: <u>5th May 2005</u>

Supervisor:

Michael Manzke

Examining Committee: \_\_\_\_

Michael Manzke

Donal O'Mahony

### UNIVERSITY OF DUBLIN, TRINITY COLLEGE

Date: 5th May 2005

| Author:              | Shonagh Hurley                      |    |

|----------------------|-------------------------------------|----|

| Title:               | The Application of Tomasulo's Metho | bd |

| Department:          | Computer Science                    |    |

| Degree: <b>B.A</b> . | Month: October Year: 200            | )5 |

Permission is herewith granted to University of Dublin, Trinity College to circulate and to have copied for non-commercial purposes, at its discretion, the above title upon the request of individuals or institutions.

Signature of Author

THE AUTHOR RESERVES OTHER PUBLICATION RIGHTS, AND NEITHER THE THESIS NOR EXTENSIVE EXTRACTS FROM IT MAY BE PRINTED OR OTHERWISE REPRODUCED WITHOUT THE AUTHOR'S WRITTEN PERMISSION.

THE AUTHOR ATTESTS THAT PERMISSION HAS BEEN OBTAINED FOR THE USE OF ANY COPYRIGHTED MATERIAL APPEARING IN THIS THESIS (OTHER THAN BRIEF EXCERPTS REQUIRING ONLY PROPER ACKNOWLEDGEMENT IN SCHOLARLY WRITING) AND THAT ALL SUCH USE IS CLEARLY ACKNOWLEDGED. To my family.

# Table of Contents

| Τa            | able o | of Con  | tents                                  | $\mathbf{V}$ |

|---------------|--------|---------|----------------------------------------|--------------|

| Li            | st of  | Tables  | 3                                      | viii         |

| $\mathbf{Li}$ | st of  | Figure  | 28                                     | ix           |

| A             | bstra  | ict     |                                        | xi           |

| A             | ckno   | wledge  | ments                                  | xii          |

| 1             | Intr   | oducti  | on                                     | ii           |

|               | 1.1    | Aim     |                                        | ii           |

|               | 1.2    | Appro   | ach                                    | ii           |

|               | 1.3    | Design  | Description                            | iii          |

|               | 1.4    | Requi   | rements                                | iii          |

| <b>2</b>      | Bac    | kgrour  | nd Research                            | v            |

|               | 2.1    | IBM S   | bystems 360                            | v            |

|               |        | 2.1.1   | Computer Family                        | v            |

|               |        | 2.1.2   | Motivation behind Tomasulo's Algorithm | vi           |

|               |        | 2.1.3   | Model 91                               | vi           |

|               | 2.2    | NASA    | and the Model 91                       | viii         |

| 3             | Adv    | vanced  | Pipelining Features                    | x            |

|               | 3.1    | Pipelin | nes                                    | х            |

|               | 3.2    | Depen   | dencies                                | xii          |

|               |        | 3.2.1   | True Data Dependencies                 | xii          |

|               |        | 3.2.2   | Name Dependencies                      | xiii         |

|               |        | 3.2.3   | Control Dependencies                   | xiii         |

|          |                                        | 3.2.4                                                                                                                      | Resource Dependencies                                                                                                                    | X111                                                                                                         |

|----------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|          | 3.3                                    | Hazaro                                                                                                                     | ls                                                                                                                                       | xiv                                                                                                          |

|          |                                        | 3.3.1                                                                                                                      | Structural Hazards                                                                                                                       | xiv                                                                                                          |

|          |                                        | 3.3.2                                                                                                                      | Data Hazards                                                                                                                             | xiv                                                                                                          |

|          |                                        | 3.3.3                                                                                                                      | Control hazards                                                                                                                          | xvi                                                                                                          |

|          | 3.4                                    | Instrue                                                                                                                    | ction Level Parallelism                                                                                                                  | xviii                                                                                                        |

|          | 3.5                                    | Dynan                                                                                                                      | nic Scheduling                                                                                                                           | xix                                                                                                          |

|          |                                        | 3.5.1                                                                                                                      | The Idea                                                                                                                                 | xix                                                                                                          |

|          |                                        | 3.5.2                                                                                                                      | Overcoming Data Hazards with Dynamic Scheduling $\ .\ .\ .$ .                                                                            | xix                                                                                                          |

| <b>4</b> | Ton                                    | nasulo'                                                                                                                    | s Method                                                                                                                                 | xxi                                                                                                          |

|          | 4.1                                    | Histor                                                                                                                     | y of Tomasulo                                                                                                                            | xxi                                                                                                          |

|          | 4.2                                    |                                                                                                                            | ulo's Algorithm                                                                                                                          | xxii                                                                                                         |

|          | 4.3                                    |                                                                                                                            | ructs of Tomasulo's Algorithm                                                                                                            | xxiv                                                                                                         |

|          |                                        | 4.3.1                                                                                                                      | Reservation Station                                                                                                                      | xxiv                                                                                                         |

|          |                                        | 4.3.2                                                                                                                      | Register Status Table                                                                                                                    | XXV                                                                                                          |

|          |                                        | 4.3.3                                                                                                                      | Common Data Bus                                                                                                                          | XXV                                                                                                          |

|          | 4.4                                    | Worke                                                                                                                      | d Example of Tomasulo's Algorithm                                                                                                        | xxvi                                                                                                         |

|          | 4.5                                    | Summ                                                                                                                       | ary                                                                                                                                      | XXXV                                                                                                         |

|          |                                        |                                                                                                                            |                                                                                                                                          |                                                                                                              |

| <b>5</b> | Soft                                   | ware a                                                                                                                     | and Hardware xx                                                                                                                          | xxvi                                                                                                         |

| 5        | <b>Soft</b><br>5.1                     |                                                                                                                            | and Hardware xx                                                                                                                          |                                                                                                              |

| 5        |                                        | Softwa                                                                                                                     |                                                                                                                                          | xxxvi                                                                                                        |

| 5<br>6   | $5.1 \\ 5.2$                           | Softwa                                                                                                                     | are - VHDL                                                                                                                               | xxxvi                                                                                                        |

| _        | $5.1 \\ 5.2$                           | Softwa<br>Hardw<br>le <b>Desi</b>                                                                                          | are - VHDL                                                                                                                               | xxxvi<br>xxxvii<br><b>xx</b> ii                                                                              |

| _        | 5.1<br>5.2<br>Cod                      | Softwa<br>Hardw<br>le Desi<br>Design                                                                                       | are - VHDL                                                                                                                               | xxxvi<br>xxxvii<br><b>xx</b> ii                                                                              |

| _        | 5.1<br>5.2<br><b>Cod</b><br>6.1        | Softwa<br>Hardw<br>le Desi<br>Design                                                                                       | are - VHDL                                                                                                                               | xxxvi<br>xxxvii<br><b>xviii</b><br>xxxviii                                                                   |

| _        | 5.1<br>5.2<br><b>Cod</b><br>6.1        | Softwa<br>Hardw<br><b>le Desi</b><br>Design<br>Indivio                                                                     | are - VHDL                                                                                                                               | xxxvi<br>xxxvii<br>cviii<br>xxxviii<br>xxxviii<br>xl<br>xl                                                   |

| _        | 5.1<br>5.2<br><b>Cod</b><br>6.1        | Softwa<br>Hardw<br>le Design<br>Individ<br>6.2.1                                                                           | are - VHDL                                                                                                                               | xxxvi<br>xxxvii<br><b>cviii</b><br>xxxviii<br>xl<br>xl<br>xl<br>xl                                           |

| _        | 5.1<br>5.2<br><b>Cod</b><br>6.1        | Softwa<br>Hardw<br>le Design<br>Individ<br>6.2.1<br>6.2.2<br>6.2.3                                                         | are - VHDL                                                                                                                               | xxxvi<br>xxxvii<br><b>cviii</b><br>xxxviii<br>xl<br>xl<br>xl<br>xl                                           |

| _        | 5.1<br>5.2<br><b>Cod</b><br>6.1        | Softwa<br>Hardw<br>le Design<br>Individ<br>6.2.1<br>6.2.2<br>6.2.3                                                         | are - VHDL                                                                                                                               | xxxvi<br>xxxvii<br>xxxvii<br>xviii<br>xl<br>xl<br>xl<br>xliii<br>xlviii                                      |

| _        | 5.1<br>5.2<br><b>Cod</b><br>6.1        | Softwa<br>Hardw<br>Design<br>Individ<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                   | gn       xxx         Introduction          Background Information          Instruction Queue          Opcode to Functional Unit Selector | xxxvi<br>xxxvii<br>xxxviii<br>xl<br>xl<br>xl<br>xliii<br>xlviii<br>li                                        |

| _        | 5.1<br>5.2<br><b>Cod</b><br>6.1        | Softwa<br>Hardw<br>le Design<br>Individ<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                                       | are - VHDL                                                                                                                               | xxxvi<br>xxxvii<br>xxxviii<br>xviii<br>xl<br>xl<br>xl<br>xliii<br>xlviii<br>li<br>lxiv                       |

| _        | 5.1<br>5.2<br><b>Cod</b><br>6.1        | Softwa<br>Hardw<br>Design<br>Individ<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6                                 | gn       xxx         Introduction                                                                                                        | xxxvi<br>xxxvii<br>xxxvii<br>xviii<br>xl<br>xl<br>xl<br>xliii<br>xlviii<br>li<br>lxiv<br>lxvi                |

| _        | 5.1<br>5.2<br><b>Cod</b><br>6.1        | Softwa<br>Hardw<br>Design<br>Individ<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>6.2.8               | are - VHDL                                                                                                                               | xxxvi<br>xxxvii<br>xxxviii<br>xviii<br>xl<br>xl<br>xl<br>xl<br>xliii<br>xlviii<br>li<br>lxiv<br>lxvi<br>lxvi |

| 6        | 5.1<br>5.2<br><b>Coc</b><br>6.1<br>6.2 | Softwa<br>Hardw<br>Design<br>Individ<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>6.2.8<br><b>iew</b> | are - VHDL                                                                                                                               | xxxvi<br>xxxvii<br>xxxviii<br>xl<br>xl<br>xl<br>xliii<br>xlviii<br>li<br>lxiv<br>lxvi<br>lxvi                |

| 7.3     | Project Conclusion | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | lxxiii |

|---------|--------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--------|

| Bibliog | graphy             |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | lxxv   |

# List of Tables

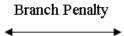

| 3.1 | Demonstrates the penalty caused by a branch                    | xvii   |

|-----|----------------------------------------------------------------|--------|

| 4.1 | Sequence of 3 instructions                                     | xxvi   |

| 4.2 | Tag and Result from CDB                                        | xxxiii |

| 6.1 | Stack form<br>at implemented in VHDL entity: Instruction Queue | xliv   |

# List of Figures

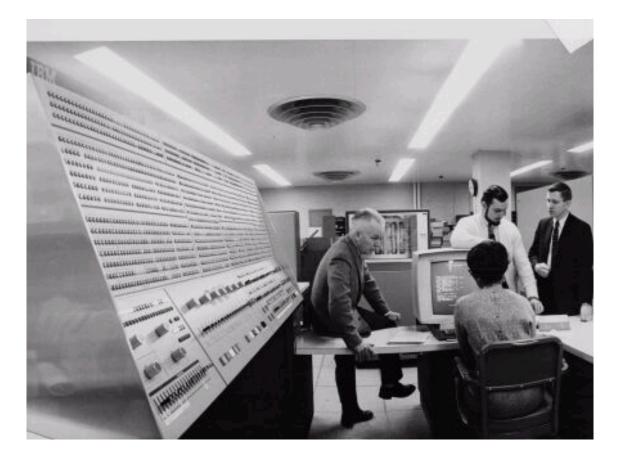

| 2.1 | The Model 91 at NASA's Goddard Space Flight Center [14]                                                                      | ix     |

|-----|------------------------------------------------------------------------------------------------------------------------------|--------|

| 3.1 | A basic pipeline                                                                                                             | xi     |

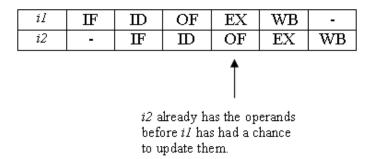

| 3.2 | $i1$ followed by $i2$ in a pipeline $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                    | XV     |

| 3.3 | Two stage stall must occur                                                                                                   | XV     |

| 3.4 | Solution to the two stage stall                                                                                              | xvi    |

| 4.1 | <b>Step 1</b> : first instruction (registering instruction)                                                                  | xxvii  |

| 4.2 | Step 2: first instruction (searching for operand values) $\ldots \ldots \ldots$                                              | xxviii |

| 4.3 | Step 3: second instruction (registering instruction) $\ldots \ldots \ldots$                                                  | xxix   |

| 4.4 | Step 4: second instruction (searching for operand values) $\ldots \ldots$                                                    | XXX    |

| 4.5 | Step 5: third instruction (registering instruction) $\ldots \ldots \ldots$                                                   | xxxi   |

| 4.6 | Step 6: third instruction (searching for operand values) $\ldots \ldots$                                                     | xxxii  |

| 4.7 | Step 7: Instruction dispatched $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                              | xxxiii |

| 4.8 | Step 8: Result comes from the CDB $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                         | xxxiv  |

| 4.9 | <b>Step 9</b> : Result from the CDB is placed in the RS's $\ldots$ $\ldots$ $\ldots$                                         | xxxiv  |

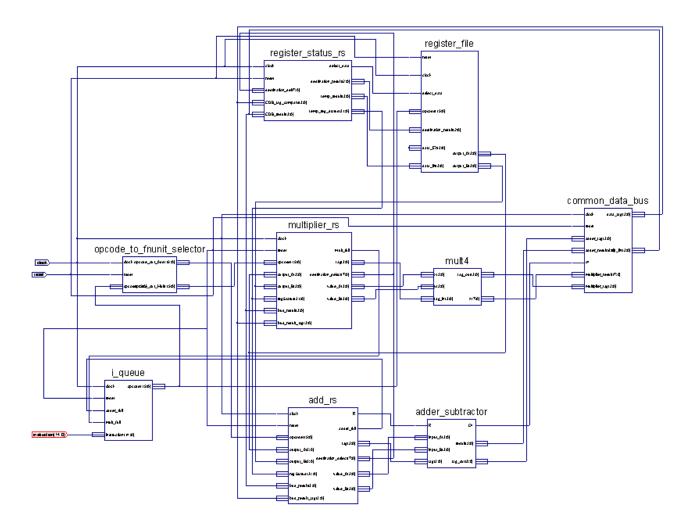

| 6.1 | Top Level Schematic                                                                                                          | xli    |

| 6.2 | Opcode                                                                                                                       | xlii   |

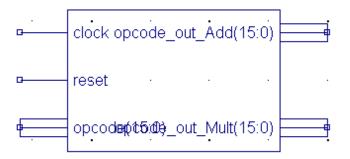

| 6.3 | opcode_to_fnUnit_selector Entity                                                                                             | xlviii |

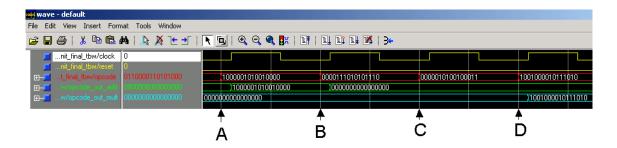

| 6.4 | Testbench waveform - opcode_to_fnUnit_selector                                                                               | xlix   |

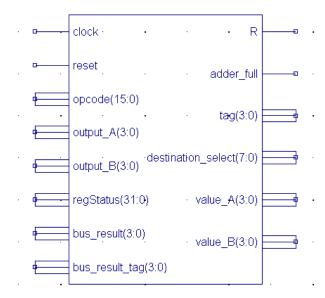

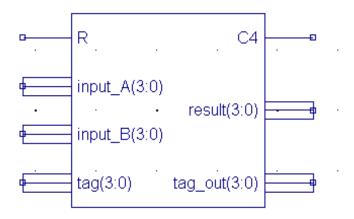

| 6.5 | $\texttt{reservation\_station} \ Entity \ \ \ldots $ | li     |

| 6.6 | Reservation Station                                                                                                          | lii    |

| 6.7  | Determining the register              | liv   |

|------|---------------------------------------|-------|

| 6.8  | Outputting the completed instruction  | lvi   |

| 6.9  | (a) Testbench Waveform - RS           | lvii  |

| 6.10 | (b) Testbench Waveform - RS           | lix   |

| 6.11 | (c) Testbench Waveform - RS $\ldots$  | lix   |

| 6.12 | Testbench Waveform - timing error     | lx    |

| 6.13 | Caused error                          | lxii  |

| 6.14 | Fixed error                           | lxiii |

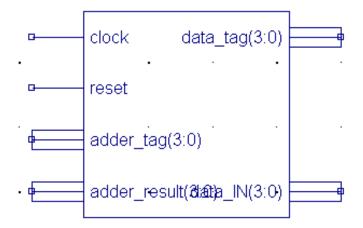

| 6.15 | adder_subtractor $Entity$             | lxiv  |

| 6.16 | Testbench Waveform - Adder/Subtractor | lxv   |

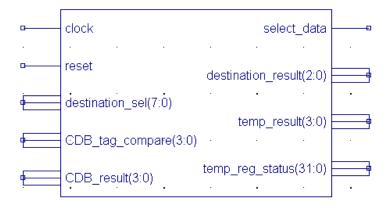

| 6.17 | common_data_bus Entity                | lxvi  |

| 6.18 | register_file Entity                  | lxvii |

| 6.19 | register_status_table Entity          | lxix  |

# Abstract

The aim of this project is to display the phenomenal impact Tomasulo's Method has had on modern day computer architecture.

To do this, a datapath implemented with hardware, proposed by the Tomasulo Method, was built in the hardware description language, VHDL<sup>2</sup>.

There are two phases to this dissertation: Firstly, the various stages of research are outlined, focusing on advanced pipelining features. Secondly, a detailed design description is given, outlining the specifications, requirements, design procedure and testing stages.

Overall, the project was very challenging and to date I have a fully simulated and synthesised version of my design. The top-level code, however, is fully functioning for only one instruction. All internal entities have been tested and a small amount of adjustment would allow application to other instructions.

<sup>&</sup>lt;sup>2</sup>VHDL: VHSIC(Very High Speed Integrated Circuit) Hardware Description Language

# Acknowledgements

I would like to thank Michael Manzke, my supervisor, for his advice, guidance, encouragement and support during this project.

Shonagh Hurley Trinity College Dublin May, 2005

# Chapter 1 Introduction

# 1.1 Aim

My main goal when undertaking this project was to ensure that I gained a fully comprehensive understanding of the mechanics of computer architecture, in particular focusing on the area of advanced pipelining features. This was achieved by building a complicated hardware model of a datapath and the extra features required to solve the prominent problems of dependencies, hazards and stalls.

# 1.2 Approach

My dissertation encompasses two areas.

Firstly it gives an in depth account of the extensive research I had to complete. Before I embarked on the task of coding such a program, it was important that I be fully comfortable and familiar with all aspects in the area of instruction level parallelism and dynamic scheduling along with the method I wished to implement.

Secondly it describes my endeavours to design a synthesisable VHDL model of a speculative integer execution core based on Tomasulo's Method.

# **1.3** Design Description

This project will implement the algorithms for dynamic scheduling and speculative execution using Tomasulo's Algorithm.

Two main features of Tomasulo's Algorithm are the implementation of reservation stations and the common data bus [11]. These in turn implement a renaming and tagging scheme, which form the fundamental principals of Tomasulo's Algorithm. The importance of these features is highlighted throughout the course of this dissertation. This design supports instructions that are used commonly in modern day processors. The instructions use 3 addresses consisting of 2 sources and 1 destination. An example of an arithmetic instruction would be:

$$R1 = R2 + R3;$$

$R4 = R3 - R5;$

$R6 = R2 * R1;$

Seeing as data transfer operations have not been implemented as of yet, a special LOAD operation has been employed in order to initialise the register file with starting values.

The instructions which are hardcoded in a binary format into a VHDL entity, called an instruction queue, are commonly referred to as opcodes [2].

The operations that are catered for so far are: addition, subtraction, multiplication and load. The appropriate functional units will be required to perform such operations. The result will be placed on to a bus. This bus will serve all units.

## **1.4 Requirements**

The program will be built in a dynamically scheduled pipelined processor where each stage performs a specific task every clock cycle.

The main aim of building such a model is to produce a sequence of correct results from instructions every clock cycle by avoiding structural, data and control hazards. Hazards exist from dependencies and the solution to this will be to implement a method proposed by Robert Tomasulo in 1967.

Multiple functional units will be employed along with a register renaming policy [1]. Functional units use reservation stations which will buffer instructions before they are executed.

The functional units employed so far are: an adder, performing both addition and subtraction, and a multiplier performing multiplication.

A single bus, called a common data bus, will also be implemented.

The function and importance of all of these will be emphasised throughout.

# Chapter 2 Background Research

# 2.1 IBM Systems 360

The Systems 360 computer family is where Tomasulo's Algorithm originated [1]. The following chapter gives an overview of how, why and when Tomasulo's Algorithm was developed.

### 2.1.1 Computer Family

The IBM<sup>1</sup> System/360 is a family of computer systems, developed in the 1960's, where the chief architect was the well known Gene Amdahl [17]. Prior to the announcement of this family, computers were custom made and designed independently. This development of computers indicated that a new revelation was underway and would change the computer industry forever.

Initially only 6 models were announced: 30, 40, 50, 60, 62, and 70, whereas in actual fact 14 models were produced: 20, 22, 25, 30, 40, 44, 50, 65, 67, 75, 85, 91, 95 and the 195 [17].

Despite the models' individual differences, the System 360 family employed the same user-instruction set. The larger machines dealt with complex instructions through

<sup>&</sup>lt;sup>1</sup>International Business Machines

hardware whilst the smaller ones dealt with them in micro-code, where such an instruction as *multiplication* would be completed by repeated addition. And as we know today, this was an extremely inefficient way to execute a multiplication instruction [10]. (It was also rumoured that the smaller 360 machines performed addition by repeated increments! (i.e.  $x + 5 \rightarrow add a 1$  bit five times!) [13]

The System 360 employed a variety of operating systems [14]:

- (i) DOS/360

- (ii) OS/360

- (iii) CP-67 (later VM/370)

- (iv) MTS

- (v) CRJE

- (vi) TSO

- (vii) Amdahl's UTS

The OS/360 proved to be the most popular.

#### 2.1.2 Motivation behind Tomasulo's Algorithm

The 360 computer family had a very limited number of registers that initially consisted of only four double precision floating-point registers. Consequently compiler scheduling was not particularly effective. On top of this, even the more optimal 360 designs took considerable time to access memory and compute long floating point equations. Due to the number of constraining factors, this prompted programmers to develop a solution, so as to attain maximum efficiency [12]. The ultimate solution to the problems comes in the form of Tomasulo's Algorithm. See section: 4.2

#### 2.1.3 Model 91

Tomasulo's Algorithm was first designed for the IBM system 360 Model 91(360/91), which produced the initial protocol in 1964, but didn't employ Tomasulo's Algorithm

until 1967. The Model 91 of the 360 family had the most advanced internal architecture of all System 360 computers and of any other computer of its time [14]. The reason behind this was that the algorithm, designed by Robert Tomasulo, supported *dynamic scheduling* and *instruction level parallelism*.

The Model 91 was specifically designed to perform high-speed data processing, directly intended for scientific purposes. Such intentions included space exploration, theoretical astronomy, subatomic physics and global weather forecasting [14].

The model had three specific advanced features, giving it the capabilities to perform speeds never before achieved.

These included:

- 1. Sophisticated circuits, which had the ability to switch in billionths of seconds

- 2. High density circuit packaging techniques

- 3. High degrees of concurrency i.e. parallel operators

These three factors were superior in the day and provided the Model 91 with the resources to perform up 16.6 million additions per second. Also said to compute more than one thousand problems a day, requiring approximately 200 billion calculations, and subsequently providing 50 times the arithmetic capacity of previous models [10]. The Central Processing Unit (CPU) also played a part in this increased processing power, as it contained five independent execution units allowing the system to process many instructions simultaneously.

The five units were:

- (i) Processor Storage

- (ii) Storage Bus Control

- (iii) Instruction Processor

- (iv) Fixed Point Processor

#### (v) Floating Point Processor.

These units had the ability to perform several functions at the same time and, additionally, all five could operate in parallel. Such designs were an incredible revelation in 1967, despite being very familiar to Computer Scientists today, and are now commonly known as *pipelining*. See section: 3.1

The Model 91 had a CPU cycle time<sup>2</sup> of 60 nanoseconds and a Memory cycle time of 780 nanoseconds [10].

# 2.2 NASA and the Model 91

The Model 91 was the first computer to be described as a supercomputer<sup>3</sup>. Initially, it was designed for the North American Missile Defence System. Interestingly, the S/360 was IBM's most expensive project, and equally its most risky. IBM bet the whole company on the 5 billion dollar project [14] (equating to 30 billion dollars in today's terms). Obviously they've never looked back.

The most expensive computer project of the 1960's was the moon exploration Apollo Program, with the IBM's S/360 bid coming in second place! However, the Apollo Program actually relied quite extensively on the System 360, and in particular on the Model 91, which was installed for this program at NASA's Goddard Space Flight Center, Greenbelt, Md.

The Model 91, operated with 2,097,152 bytes of main memory, interleaved 16 ways and could accommodate 6,291,496 bytes of main storage. It could also store more than 300 million characters in 2 drum and direct access storage units [10]. It was the fastest and most powerful computer. See figure: 2.1

$<sup>^{2}</sup>$  cycle time: the time that elapses from the beginning to the end of a process

<sup>&</sup>lt;sup>3</sup>The class of fastest and most powerful computers available

Figure 2.1: The Model 91 at NASA's Goddard Space Flight Center [14]

# Chapter 3 Advanced Pipelining Features

# 3.1 Pipelines

Pipelining is one of the most useful methods in increasing processor speed and composes the basic structure of most modern general purpose computers. The pipeline design breaks down a sequence of processes into a number of sub processes. These sub processes can be identified as a *stage*. Each stage has a specific task, performing a particular function and producing an immediate result.

When coding a pipeline in hardware, latches (or registers) are employed to enable the flow of instructions. At the end of each clock cycle, each stage sends its results into the latches at the end of the stage. The latches hold these results for use of the stage coming immediately after the latch [7].

In a classic pipeline there are five stages:

- 1. IF (Instruction Fetch)

- fetches the instruction pointed to by the Program Counter (PC)

- increments the PC

- 2. ID (Instruction Decode)

- decodes the instruction (opcode)

- 3. OF (Operand Fetch)

- fetches the required sources

- 4. EX (Execute)

- performs the operation

- 5. WB (Write Back)

- writes the results to the destination register

See figure: 3.1

|                |   | Clock cycles |    |    |    |    |    |    |  |  |  |  |

|----------------|---|--------------|----|----|----|----|----|----|--|--|--|--|

|                |   | 1            | 2  | 3  | 4  | 5  | 6  | 7  |  |  |  |  |

| [              | İ | IF           | ID | OF | EX | WB |    |    |  |  |  |  |

| instructions { | j |              | IF | ID | OF | EX | WB |    |  |  |  |  |

| Ĺ              | k |              |    | IF | ID | OF | EX | WB |  |  |  |  |

Figure 3.1: A basic pipeline

In the pipeline above, instruction i begins in the **first clock cycle**, and fetches its instruction.

In clock cycle 2, j begins, fetching its instruction, whilst i decodes its own instruction.

In clock cycle 3, k begins, fetching its instruction, whilst j decodes, and i fetches its operands.

In clock cycle 4, i executes, whilst j fetches its operands and k decodes its instruction.

In clock cycle 5, i has completed and writes the result, whilst j executes and k fetches its operands.

In clock cycle 6, j writes it result whilst k executes.

And in clock cycle 7, k writes its result.

Pipelines imply an in-order-execution process, disallowing one instruction to bypass another and making full use of the CPU. Therefore an out-of-order dynamic scheduling algorithm is used, which will be explained in more detail.

The Tomasulo Algorithm, despite being modelled around the classic 5 stage pipeline, employs only 3 stages:

- 1. Issue: get instructions from the instruction queue

- 2. Execute: perform operation on operands

- 3. Write Result: finish execution, i.e. write result

See detailed explanation in section: 4.2

## **3.2** Dependencies

Dependencies, which are simply scheduling constraints, are properties of programs. i.e. if two instructions are data dependent, they cannot execute simultaneously. A dependency results in a hazard.

#### 3.2.1 True Data Dependencies

An instruction, i, is dependent on an instruction, j, when the following conditions hold:

- 1. Instruction, i, writes to a destination that instruction, j, uses as a source.

- Instruction, j, is data dependent on instruction, k, which is data dependent on instruction i.

#### 3.2.2 Name Dependencies

A name dependence occurs between two instructions using the same register or memory location, however no data flow exists between them. There are two different types of name dependencies.

Anti-dependence: When instruction j writes to a register or memory location that instruction i uses as a source.

**Output-dependence**: When instruction i and j write to the same register or memory location, the ordering must be preserved to ensure the correct value is in the register.

*i* ADD R7, R4, R3 *j* ADD R7, R2, R8

#### 3.2.3 Control Dependencies

A control dependence determines the ordering of an instruction, with respect to a branch instruction so that the instruction is executed in correct program order.

#### 3.2.4 Resource Dependencies

An instruction is resource dependent on a previously issued instruction if it requires a hardware resource which is still being used by a previously issued instruction. Tomasulo's Algorithm is not overly concerned by this dependency.

There are two ways in which dependencies are checked:

- Statically by the compiler at compile time. *or*

- Dynamically by the hardware at run time.

The compiler can sometimes overlook dependencies, as not all operations will have addresses at compile time. Dynamically checking however should catch most dependencies. One of the most common techniques of dynamic dependency checking is Tomasulo's Method.

## 3.3 Hazards

One of the major issues of pipelining is hazards. A hazard prevents a correct program from functioning properly. Hazards are a result of a dependency. There are three types of hazards:

#### 3.3.1 Structural Hazards

Structural Hazards exist when two or more instructions try to use the same resource at the same time. For example if a register file has only one read/write port, then a pipeline wanting to perform 2 register writes in one clock cycle, is not able to. A solution to this is to add more hardware i.e. use register files with multiple input/output ports or, as in my design, implement multiple execution units.

#### 3.3.2 Data Hazards

If an instruction requires the result of a previously issued instruction, but this previously issued instruction has not yet been completed, then a data hazard exists. Data hazards can be eliminated by forwarding or bypassing. (Discussed in detail below.)

There are three primary types of data hazards:

• Read after Write Hazards (RAW)

| i1 | ADD R2, F | R2, R4 | R2 = R2 + R4 |

|----|-----------|--------|--------------|

| i2 | ADD R5, F | R2, R1 | R5 = R2 + R1 |

Instruction, i2 can only read from R2 *after* instruction i1 has successfully written to it, so as i2 obtains the most updated register value. See the following diagrams:

Figure 3.2: i1 followed by i2 in a pipeline

| il | IF | ID | OF | EX | WB |    |    |    |

|----|----|----|----|----|----|----|----|----|

| i2 |    | IF | ID |    |    | OF | ΕX | WB |

Figure 3.3: Two stage stall must occur

i2 must wait until i1 has written back before it fetches its operands.

|                  | il | IF | ID | OF | ΕX | WB |    |    |    |

|------------------|----|----|----|----|----|----|----|----|----|

| 2 independent    | i3 |    | IF | D  | OF | EX | WB |    |    |

| instructions can | i4 |    |    | IF | ID | OF | EX | WB |    |

| be inserted.     | i2 |    |    |    | IF | ID | OF | ΕX | WB |

Figure 3.4: Solution to the two stage stall

• Write after Read Hazards (WAR)

| i1 | ADD R2, R3, R4 | R2 = R3 + R4 |

|----|----------------|--------------|

| i2 | ADD R4, R5, R6 | R4 = R5 + R6 |

Instruction *i*<sup>2</sup> can only write to the register R4 after *i*<sup>1</sup> has read from it.

• Write after Write Hazards (WAW)

| i1 | ADD R2, | R3, | R4 | R2 | = | RЗ | + | R4 |

|----|---------|-----|----|----|---|----|---|----|

| i2 | ADD R2, | R5, | R6 | R2 | = | R5 | + | R6 |

Instruction *i*<sup>2</sup> must write to register R2 *after i*<sup>1</sup> has written to it, so as the most up-to-date value is obtained.

#### 3.3.3 Control hazards

When a branch is taken, the pipelines performance is seriously affected as it must essentially drain and refill.

Time is needed to load the Program Counter (PC) with the target address when a branch or a jump is taken. An instruction such as a branch causes a change in the program flow.

The Branch instruction requires a new address to be loaded into the PC, which could

also have detrimental effects on all other instructions by invalidating them.

There are three branch types:

- **Unconditional**: An unconditional branch will always alter the sequential flow of a program. It will set the new target address in the PC.

- **Conditional**: A condition must be satisfied for the branch to be taken. If it is satisfied, then a new target address is sent in and the PC points to it. These branches are the hardest to handle.

- **Loop**: This type of branch causes the program to jump back to a particular point in the program and execute it 'n' number of times.

| IF | ID | OF | EX | WB |    |    |    |    |    |

|----|----|----|----|----|----|----|----|----|----|

|    | IF | ID | OF |    |    |    |    |    |    |

|    |    | IF | ID |    |    |    |    |    |    |

|    |    |    | IF |    |    |    |    |    |    |

|    |    |    |    | IF | ID | OF | EX | WB |    |

|    |    |    |    |    | IF | ID | OF | EX | WB |

Table 3.1: Demonstrates the penalty caused by a branch

A solution to control hazards is to correctly predict the flow of the program by a technique called *Branch Prediction*. There are two other solutions sometimes used to solve these hazards: delayed branching and multiple prefetching.

#### Solution to hazards:

A general solution to eliminate hazards is to stall the pipeline until the hazard has been resolved itself. However, we unquestionably want to avoid this, as it causes degradation to the CPU's throughput<sup>1</sup>.

Stalls due to the above three hazards increase the  $CPI^2$  for the pipeline:

It is necessary to minimize stalls to get maximum efficiency from the pipeline. To do this, we determine which instructions can be performed in parallel without causing any hazards.

## 3.4 Instruction Level Parallelism

The execution of multiple instructions, simultaneously, in a processor is called Instruction Level Parallelism (ILP). ILP provides the basic fundamentals of modern day processors [1]. It allows the overlap of individual machine operations.

With very few exceptions, all microprocessors today are out-of-order issue *super-scalar*<sup>3</sup> processors. These processors follow a cycle of fetching, scheduling and issuing of instructions. With each generation of Information Technology, we see increasingly advanced features being added to exploit ILP.

But why this huge success for superscalar processors?

• They execute code without the need to recompile.

<sup>&</sup>lt;sup>1</sup>Number of instructions completed in one clock cycle

<sup>&</sup>lt;sup>2</sup>Clock cycles per instruction

<sup>&</sup>lt;sup>3</sup>Hardware designs that support simultaneous processing of multiple instructions.

- They can make use of runtime information to their advantage.

- They can exploit speculative techniques, such as data, value, address and dependencies predictions.

Due to these characteristics, for the foreseeable future, superscalar processors will dominate.

# 3.5 Dynamic Scheduling

Dynamic Scheduling is the execution of sequential programs out-of-order. It is a hardware technique used to better exploit Instruction Level Parallelism. Dynamically scheduled machines were termed superscalar computers in the 1980's.

#### 3.5.1 The Idea

Pipelines, as previously mentioned, execute instructions strictly in the same order as they are inputted. Therefore, if one instruction stalls, all following instructions will stall. Dynamic Scheduling allows instructions to bypass each other. They are issued in-order in the first stage but executed out-of-order in the second stage by overtaking one another if a leading instruction stalls.

#### 3.5.2 Overcoming Data Hazards with Dynamic Scheduling

Dynamically Scheduled Algorithms are implemented in the hardware. They determine which instruction will be executed next. The order of execution is based on the availability of the operands.

There have been various proposals for such schemes; - Thornton's Scoreboarding method and Tomasulo's Algorithm are the most well known today.

Thornton's technique is simple and centralised. It relies on a portion of hardware that acts like a scoreboard. The scoreboard monitors the functional units and instructions waiting to be issued.

Unlike the sophisticated algorithm developed by Tomasulo, this technique does not remove hazards, it only avoids them, by allowing highly inefficient stalls.

# Chapter 4 Tomasulo's Method

# 4.1 History of Tomasulo

Tomasulo's Method is named after the computer architect, Robert Tomasulo, who designed the floating point unit for the IBM 360/91 [9]. Tomasulo was an architect for IBM. In 1967 he published a paper which proposed a method that resolved hazards in the datapath of the processor. Prior to this, processors only had the ability to avoid hazards as opposed to fully solving them.

Today, a very large number of microprocessors use Tomasulo's Method to implement out-of-order execution, including the full series of Pentium Processors.

In 1997, Tomasulo received the Eckert-Mauchly Award [16] for his outstanding contributions to the field of computer and digital systems architecture. Specifically titled *"For the ingenious Tomasulo's algorithm, which enabled out-of-order execution processors to be implemented"*. This is an award granted by the ACM<sup>1</sup> and the IEEE<sup>2</sup> Computer Society. It has been said that this was a very long awaited award, and deserved well before the year it was presented, considering the phenomenal impact it has had on today's computer architecture.

<sup>&</sup>lt;sup>1</sup>Association for Computing Machinery

<sup>&</sup>lt;sup>2</sup>Institute of Electrical and Electronics Engineers

# 4.2 Tomasulo's Algorithm

In brief, Tomasulo's Algorithm supports in-order issuing and out-of-order execution of machine level code. The instructions are dispatched to the datapath in a particular sequence but leave the datapath in an entirely different order - the aim being to execute the instructions according to *dataflow* as opposed to *sequential order*. The question then is: How do we maintain this data consistency throughout the sequence of instructions?

The method proposed by Tomasulo uses an intelligent *renaming* method and *operand tracking* system, to resolve hazards and dependencies. This is implemented through a sophisticated tagging scheme.

Tomasulo began with two functional units: an adder/subtractor and a multiplier/divider. He recognized that the relationship between a current instruction and all incomplete instructions must be distinguished so as to determine any existing dependencies. He could then realize his main objective, which was to preserve essential precedences while allowing the greatest possible overlap of independent operations [9]. Tomasulo states three requirements that must be maintained:

- 1. Recognize the existence of a dependency

- 2. Cause the correct sequencing of the dependent instructions

- 3. Distinguish between the given sequence.

Points number 1. and 2. must be maintained to preserve the integrity of the program, while point 3. is required to meet the performance goal [9].

This original proposal was limited to 2-address instructions (1 source and 1 destination, R3 += R4). However it can be easily extended to handle 3-address instructions (R2 + R5 = R7), as are used in most processors today. It also did not support interrupts. However, a re-order buffer may be implemented to deal with these [15]. Upon an instruction entering the datapath, it receives a tag. This tag will stay with the instruction as it travels through from its initial stage of "issue" to its final stage of "write back".

These tags are determined by a hardware device called a *Reservation Station*(RS). An RS stores an instruction until it has the values A and B that are required for the instruction to execute. The instruction will sit in the reservation station whilst it gathers the required values, using the information provided by the opcode.

There are a number of locations in an RS, so multiple instructions can be stored. Each of these locations has a unique identity tag. It is this identity tag, that attaches itself to all registers associated with the particular instruction. It enables the design to maintain data consistency throughout the entire sequence execution.

To explain the algorithm as concisely as possible I have outlined the main functions of the extra units needed to implement such a design. In the following section we will work through a concrete example.

The tagging system enables the continuous tracking of operands which minimizes RAW hazards, and the register renaming minimizes the number of WAW and RAW hazards.

This method has two major advantages over previous schemes [1].

- 1. **Distribution of hazard detection logic:** achieved from the distributed reservation stations and the common data bus

- 2. Elimination of stalls for WAW and WAR hazards: achieved by register renaming and by the process of storing operands into the reservation stations.

As mentioned in Section 3.1, the Classic Pipeline executes in five stages, whereas Tomasulo's Algorithm implements only three stages:

#### 1. Instruction Issue:

An instruction is sent from the instruction queue if, and only if, there is an

empty space in the appropriate reservation station. If the operand values exist in the register file, they are sent to the reservation station. If the operation is a load or store, the value is issued if there is an available buffer. The registers are renamed (or tagged in the case of Tomasulo's Method) if required. If there is no empty reservation station or buffer, then an unpreventable structural hazard occurs.

#### 2. Execute:

If operations have not arrived at the reservation station to complete an instruction, the common data bus is snooped<sup>3</sup> for values. When a value becomes available, it is placed in all units that require it. When the reservation station has both operand values, the instruction is sent to the functional unit and executed.

#### 3. Write Result:

When the functional unit has executed the instruction, the result is written to the common data bus and then to the reservation stations where required.

# 4.3 Constructs of Tomasulo's Algorithm

#### 4.3.1 Reservation Station

There is a reservation station (RS) for each of the functional units in the model. Essentially a reservation station is a buffer. It stores an issued instruction awaiting operands. It holds these instructions until the instruction has received the operand values it requires for execution.

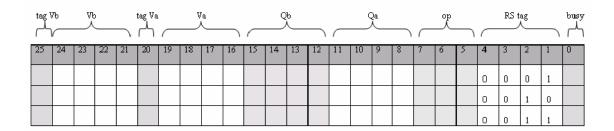

In my code the fields in the RS are as follows: A *busy* bit to indicate if a particular slot in the RS is available for an instruction to be held. An *op* field to determine what operation will be executed. Qa and Qb fields, which determine where the value

<sup>&</sup>lt;sup>3</sup>continually monitor

A or value B will come from. Va and Vb fields, indicating the exact value of A or B. And also a Tag Va and Tag Vb fields, which signify when the actual values of the operands have been obtained. There is also a unique tag in the RS to identify the various slots available. This unique tag is attached to the destination register in the Register Status Table.

#### 4.3.2 Register Status Table

The Register Status Table (RST) is a piece of hardware attached to the register file. It is similar to a RS as it buffers information for the unit it is associated with.

Each register has an associated tag field in the RST. This 4 bit tag indicates which RS the value will come from and also determines whether or not a register is waiting for a more up-to-date value or whether it has an actual valid value. The tag indicates which RS the value will come from.

As the functional unit's RS's are filling up with the required information they will consult the RST to see if it is permissible or not to take the value in the desired register. If it is, the value is placed in the V field; if it is not, the tag is placed in the Q field.

#### 4.3.3 Common Data Bus

The common data bus receives its inputs (values) from the functional units. Upon receiving a result from a functional unit, the common data bus sends the result to all units via their reservation stations (except the Load unit) and as a result speeds up the execution by bypassing the architectural registers.

### 4.4 Worked Example of Tomasulo's Algorithm

To explain the the internal workings of Tomasulo's Method, I will outline how the two most important tables manage the instructions to be executed.

The tables will be shown step by step, from holding no information to managing instructions at the RS's full capacity.

Firstly we take a simple sequence of machine code:

| ADD | R2, | R4, | RO |

|-----|-----|-----|----|

| SUB | R3, | R6, | R2 |

| ADD | R5, | R3, | R2 |

| instruction | operation | destination | source 1 | source 2      |

|-------------|-----------|-------------|----------|---------------|

| <i>i1</i>   | ADD       | R2          | R4       | R0            |

| i2          | SUB       | R3          | R6       | $\mathbf{R2}$ |

| i3          | ADD       | R5          | R3       | R2            |

Table 4.1: Sequence of 3 instructions

Instructions are dispatched from the instruction queue in-order. It is in the reservation station where the order changes.

The first instruction ADD R2, R4, R0 (R2 = R4 + R0) is sent to the reservation station.

There are two main stages in the management of an instruction. (For stage 1 of the first instruction, see the associated table labelled step 1. For stage 2 of the first instruction see the associated table labelled step 2. For stage 1 of the second instruction, see associated table labelled step 3. etc.)

- Declare the first available RS location as busy. In this case Add 1 is declared as busy.

- Set the destination register, R2, as **busy** by sending the RS name (*unique* tag) to the RST.

In this example, the *tag* for the Add 1 location is sent to R2's tag in the RST. From this point in time, any instruction that requires to read from this register, R2, will now only read the *tag* value. (When a *tag* value exists in the RST, it signifies that the *actual* value currently held in the register is no longer up-to-date, and it is waiting for an instruction to execute and write the result back.)

• The type of operation, ADD, is also recorded by the RS (this information will then be forwarded to the functional unit, when the instruction is ready.)

See figure: 4.1.

#### **Reservation Station and Register Status Table**

| Name  | Busy | Ор  | Qa | Qb | Va | Tag Va | Vb | Tag Vb |

|-------|------|-----|----|----|----|--------|----|--------|

| Add 1 | yes  | ADD |    |    |    |        |    |        |

| Add 2 |      |     |    |    |    |        |    |        |

| Add 3 |      |     |    |    |    |        |    |        |

| Reg  | R0 | R1 | R2    | R3 | R4 | R5 | R6 | <b>R</b> 7 |

|------|----|----|-------|----|----|----|----|------------|

| Busy |    |    | Add 1 |    |    |    |    |            |

Figure 4.1: Step 1: first instruction (registering instruction)

- 2. Search for *actual* operand values. Source registers are identified by reading the opcode.

- Source 1: Check the status of the register, R4, in the RST. If the register's tag is clear then the RS can read in the *actual* value held in the register.

In this example, the status of R4 is checked; it is clear. Therefore the actual value is placed in the Va field. The Tag Va field is also set to signify that source 1 has been obtained.

• Source 2: Check the status of the register, R0, in the RST. It too is clear. Therefore the actual value is placed in the Vb field. The Tag Vb field is also set to signify that source 2 has been obtained.

See figure: 4.2.

#### **Reservation Station and Register Status Table**

|   | Name  | Busy | Ор  | Qa | Qb | Va       | Tag Va | Vb       | Tag<br>Vb |

|---|-------|------|-----|----|----|----------|--------|----------|-----------|

| ſ | Add 1 | yes  | ADD |    |    | Regs[R4] | yes    | Regs[R0] | yes       |

|   | Add 2 |      |     |    |    |          |        |          |           |

|   | Add 3 |      |     |    |    |          |        |          |           |

|   | Reg  | R0 | R1 | R2    | R3 | R4 | R5 | R6 | <b>R</b> 7 |

|---|------|----|----|-------|----|----|----|----|------------|

| ſ | Busy |    |    | Add 1 |    |    |    |    |            |

Figure 4.2: Step 2: first instruction (searching for operand values)

The second instruction SUB R3, R6, R2 (R3 = R6 - R2) is sent to the reservation station.

- The first RS location Add 1 is already occupied, so Add 2 is checked. It is free and the instruction claims the location by declaring it as busy.

- Next, the destination register, R3, is set as **busy** by sending the RS name (*unique tag*) to the RST. In this example, the *tag* for the Add 2 location is sent to R3's tag in the RST. From this point in time, any instruction that requires to read from this register, R3, will now only read the *tag* value.

- The type of operation, SUB, is also recorded by the RS.

See figure: 4.3.

| Name  | Busy | Op  | Qa | Qb | Va       | Tag Va | Vb       | Tag |

|-------|------|-----|----|----|----------|--------|----------|-----|

|       |      |     |    |    |          |        |          | Vb  |

| Add 1 | yes  | ADD |    |    | Regs[R4] | yes    | Regs[R0] | yes |

| Add 2 | yes  | SUB |    |    |          |        |          |     |

| Add 3 |      |     |    |    |          |        |          |     |

**Reservation Station and Register Status Table**

| Reg  | R0 | R1 | R2    | R3    | R4 | R5 | R6 | <b>R</b> 7 |

|------|----|----|-------|-------|----|----|----|------------|

| Busy |    |    | Add 1 | Add 2 |    |    |    |            |

Figure 4.3: Step 3: second instruction (registering instruction)

- 2. Search for *actual* operand values.

- Source 1: Check the status of the register, R6, in the RST. In this example, R6 is clear. Therefore the actual value is placed in the Va field. The Tag Va field is also set to signify that source 1 has been obtained.

- Source 2: Check the status of the register, R2, in the RST.

It, however, is not clear. Therefore the tag value associated with R2 is placed in the Qb field. The RS will have to hold this instruction until this tag has been cleared. The way in which this tag is cleared and the *actual* value obtained will be described in detail further on.

See figure: 4.4.

Add 3

| Name  | Busy | Op  | Qa | Qb    | Va       | Tag Va | Vb       | ſ |

|-------|------|-----|----|-------|----------|--------|----------|---|

|       |      |     |    |       |          |        |          |   |

| Add 1 | yes  | ADD |    |       | Regs[R4] | yes    | Regs[R0] |   |

| Add 2 | yes  | SUB |    | Add 1 | Regs[R6] | yes    |          | Ī |

**Reservation Station and Register Status Table**

| Reg  | R0 | R1 | R2    | R3    | R4 | R5 | R6 | <b>R</b> 7 |

|------|----|----|-------|-------|----|----|----|------------|

| Busy |    |    | Add 1 | Add 2 |    |    |    |            |

Figure 4.4: **Step 4**: second instruction (searching for operand values)

Tag Vb yes

The third instruction ADD R5, R3, R2 (R5 = R3 - R2) is sent to the reservation station.

- The first and second RS locations are already occupied, so Add 3 is checked. It is free and so the instruction claims the location by declaring it as busy.

- Next, the destination register, R5, is set as **busy** by sending the RS name (*unique tag Add 3*) to the RST.

- The type of operation, ADD, is also recorded by the RS.

See figure: 4.5.

| Name  | Busy | Ор  | Qa | Qb    | Va       | Tag Va | Vb       | Tag<br>Vb |

|-------|------|-----|----|-------|----------|--------|----------|-----------|

| Add 1 | yes  | ADD |    |       | Regs[R4] | yes    | Regs[R0] | yes       |

| Add 2 | yes  | SUB |    | Add 1 | Regs[R6] | yes    |          |           |

| Add 3 | yes  | ADD |    |       |          |        |          |           |

| Reg  | R0 | R1 | R2    | R3    | R4 | R5    | R6 | <b>R</b> 7 |

|------|----|----|-------|-------|----|-------|----|------------|

| Busy |    |    | Add 1 | Add 2 |    | Add 3 |    |            |

Figure 4.5: Step 5: third instruction (registering instruction)

- 2. Search for *actual* operand values.

- Source 1: Check the status of the register, R3, in the RST.R3 is not clear. Therefore the tag in the RST is sent to the Qa field.

- Source 2: Check the status of the register, R2, in the RST. It too is not clear. Therefore the tag value associated with R2 in the RST is placed in the Qb field.

See figure: 4.6.

#### **Reservation Station and Register Status Table**

| Name  | Busy | Ор  | Qa    | Qb    | Va       | Tag Va | Vb       | Tag<br>Vb |

|-------|------|-----|-------|-------|----------|--------|----------|-----------|

| Add 1 | yes  | ADD |       |       | Regs[R4] | yes    | Regs[R0] | yes       |

| Add 2 | yes  | SUB |       | Add 1 | Regs[R6] | yes    |          |           |

| Add 3 | yes  | ADD | Add 2 | Add 1 |          |        |          |           |

| Reg  | R0 | R1 | R2    | R3    | R4 | R5    | R6 | <b>R</b> 7 |

|------|----|----|-------|-------|----|-------|----|------------|

| Busy |    |    | Add 1 | Add 2 |    | Add 3 |    |            |

Figure 4.6: **Step 6**: third instruction (searching for operand values)

When all locations of an RS are occupied, a signal is sent to the instruction queue to tell it not to dispatch any more instructions to that RS.

Once the RS has both values required for the instructions execution, the instruction is sent to the functional unit and the RS location is freed up for another instruction to enter.

When an instruction is sent to the functional unit, the unique tag of the RS is also sent. The instruction is executed and the result (along with the tag) is placed on the common data bus (CDB). This bus will serve all RS's avoiding the need to store the results in the register file first.

When a result and tag comes in from the CDB, the RS compares the bus' tag with all the tags held in the RS. If there is a match, the tag is cleared and the result is placed in the V field.

#### Example continued...

The instruction in Add 1 has been dispatched from the RS, as it had both its *actual* values. The instruction executes in the functional unit and is placed on the common data bus. See figure: 4.7.

**Reservation Station and Register Status Table**

| Name  | Busy | Ор  | Qa    | Qb    | Va       | Tag Va | Vb | Tag Vb |

|-------|------|-----|-------|-------|----------|--------|----|--------|

| Add 1 | no   |     |       |       |          |        |    |        |

| Add 2 | yes  | SUB |       | Add 1 | Regs[R6] | yes    |    |        |

| Add 3 | yes  | ADD | Add 2 | Add 1 |          |        |    |        |

| Reg  | R0 | R1 | R2    | R3    | R4 | R5    | R6 | <b>R</b> 7 |

|------|----|----|-------|-------|----|-------|----|------------|

| Busy |    |    | Add 1 | Add 2 |    | Add 3 |    |            |

Figure 4.7: Step 7: Instruction dispatched

The common data bus then sends the result along with the tag to all the RS's.

| Tag   | Result   |

|-------|----------|

| Add 1 | Regs[R2] |

Table 4.2: Tag and Result from CDB

All the tags in the RS's are checked to see if they match the tag from the CDB. See figure: 4.8.

| Name   | Busy | Ор  | Qa    | Qb    | Va       | Tag Va | Vb | Tag Vb     |

|--------|------|-----|-------|-------|----------|--------|----|------------|

| Add 1  | no   |     |       |       |          |        |    |            |

| Add 2  | yes  | SUB |       | Add 1 | Regs[R6] | yes    |    |            |

| Add 3  | yes  | ADD | Add 2 | Add 1 |          |        |    |            |

| Match! |      |     |       |       |          |        |    |            |

| Reg    | R0   | R1  | R2    | R3    | R4       | R5     | R6 | <b>R</b> 7 |

**Reservation Station and Register Status Table**

Busy

| Figure 4.8: St | ep 8: | Result | comes | from | the | CDB |

|----------------|-------|--------|-------|------|-----|-----|

|----------------|-------|--------|-------|------|-----|-----|

Add 2

Add 3

Add 1

When a match is found, the *actual* result is placed into the V fields in the RS and the tag in the RST is cleared.

We can also see that the instruction in Add 2 is now ready to be dispatched, as both its V fields have been filled, indicated by the Tag Va and Vb fields. See figure: 4.9.

**Reservation Station and Register Status Table**

| Name  | Busy | Ор  | Qa    | Qb | Va       | Tag Va | Vb       | Tag<br>Vb |

|-------|------|-----|-------|----|----------|--------|----------|-----------|

| Add 1 | no   |     |       |    |          |        |          |           |

| Add 2 | yes  | SUB |       |    | Regs[R6] | yes    | Regs[R2] | yes       |

| Add 3 | yes  | ADD | Add 2 |    |          |        | Regs[R2] | yes       |

| Reg  | R0 | R1 | R2 | R3    | R4 | R5    | R6 | <b>R</b> 7 |

|------|----|----|----|-------|----|-------|----|------------|

| Busy |    |    |    | Add 2 |    | Add 3 |    |            |

Figure 4.9: Step 9: Result from the CDB is placed in the RS's

## 4.5 Summary

To sum up, the main points to note on Tomasulo's Algorithm are:

- The reservation station provides hazard detection and execution control.

- Results are passed directly to functional units rather than through the registers.

- A common data bus allows all units waiting for an operand to be loaded simultaneously.

# Chapter 5 Software and Hardware

## 5.1 Software - VHDL

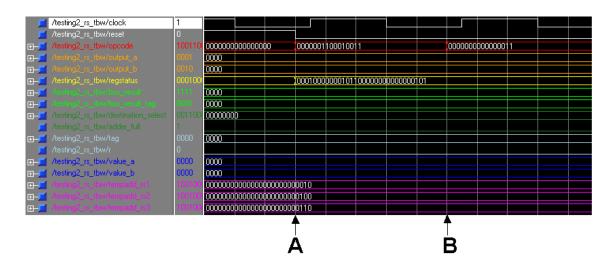

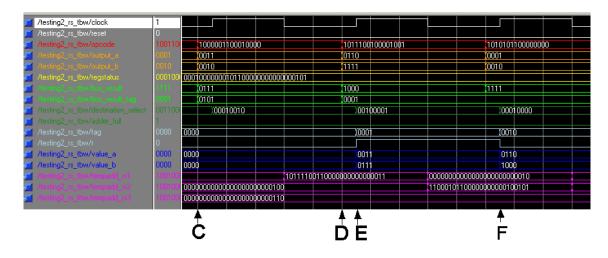

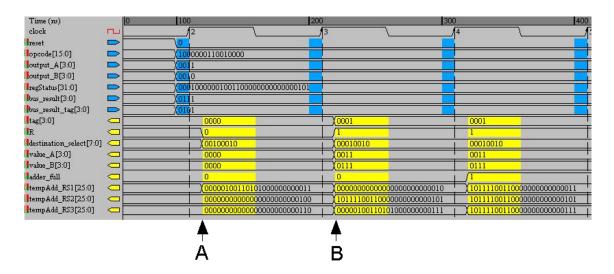

The software I chose to design my project was VHDL (VHSIC<sup>1</sup> Hardware Description Language). VHDL is a standard HDL regulated by the IEEE. It is used to describe the structure and behaviour of digital systems. A logic synthesis tool "Model Sim" is used to simulate (execute) the design. It provides us with an interface in which the values of the inputs and outputs of the design are displayed. The approach used in the design of hardware is a bottom-up approach where the design is described at primitive gate levels and built up from there to form 'entities'. Many entities are created and then connected in a top-level design. Once an entity is created it can be synthesised and simulated to check for any errors. Once the code runs at a synthesisable and simulated form, a 'testbench' is then created to verify the functionality of the code.

A testbench was created for each of my entities to guarantee the accuracy of my design. Testbench waveforms are very useful as we can verify the correctness of the circuit without having to build the circuit and test on the chip.

#### Synthesis

Synthesis is a process of transformation where the algorithmic abstract design is

<sup>&</sup>lt;sup>1</sup>Very High Speed Integrated Circuit

xxxvii

translated into a detailed structural model of gates and optimized at that level. [8] **Simulation**

Simulation is a process where the coded design is analyzed under a set of conditions. This is carried out by specifying the possible inputs and outputs into the design. The simulation software "Model Sim" then executes the design under the conditions and produces the outputs. These are manually checked from a testbench waveform (examples are explained in detail in Section: 6.2) to see if the expected results have been achieved. [8]

Both of these processes were of utmost importance in ensuring my project was functioning as expected.

## 5.2 Hardware - FPGA

An FPGA (Field Programmable Gate Array)<sup>2</sup> is a reprogrammable integrated circuit board. The FPGA in which my design had to be fully compliant with was the FPGA SPARTAN XC3 S1000.

$<sup>^{2}</sup>$ An Integrated Circuit board which can be programmed by downloading code on to it

## Chapter 6

## Code Design

## 6.1 Design Introduction

The design of my project was broken down into a number of steps:

#### Concept

The concept had to be established by analysis of all the available theory, outlined in chapters 2 through 5.

#### Specifications

The specifications had to be verified. It was very important to ensure that my design be fully compliant with the FPGA SPARTAN XC3 S1000 hardware provided by Trinity College.

Hardware designers, whilst coding through software are encouraged to "always think hardware", as code would be useless if it was not possible to implement it.

Therefore, even though downloading the project to the board was not the 'aim', the design still had to be built to a fully synthesisable and simulated form so as it could potentially be downloaded on to an FPGA.

#### Algorithm Design

This involved the design of the algorithms and the hardcode. This stage took up an extensive amount of the design time.

The hardcoded design has been done in two stages:

- 1. Design and code

- 2. Test and fix (redesign)

Whilst designing my code and writing the first draft of entities I came across many problems, both in design and syntactical.

The *design* errors were mostly resolved by writing down examples and trying different prototypes for different algorithms. I found many of these problems could also be solved by spending time working through my original prototypes of the design in my head or on paper. At that stage I could see where any glitches or errors occured, and redesign and fix accordingly.

Many of the *syntactical* errors were resolved by searching books from the library, the internet and talking to fellow VHDL'ers!

#### **Design Entry**

The top-level design then had to be entered into the FPGA design system. This is done by means of a schematic (See figure: 6.1) and top level design code.

#### Synthesis

The next stage is logic synthesis, where the built in logic synthesis tool converts the high level HDL into primitive blocks of logic.

#### Simulation

Following this is the simulation stage which checks for correct synthesis of the design in accordance with the specifications. It was here that I was faced with many timing issues. I had to repeat the Design Entry stage, fix errors, change constructs and re-synthesis and re-simulate.

#### Testing

When I began the initial phase of testing I found that many sections of my code didn't work exactly as I expected them to.

Many parts had to be redesigned or reordered, including many constructs so as optimal timing was achieved and results produced in the desired clock cycle and so forth. It is these problems where I feel I benefited most on the learning curve - and it is these errors which I will discuss throughout this chapter.

### 6.2 Individual Entity Description

In this section I will explain each individual entity as they are designed in my code. Below is the top-level schematic of the overall design. To fully understand and follow the true internal workings of the individual entities it will be necessary to refer back to this schematic. See figure: 6.1 Each entity will be described by listing the inputs and outputs, and giving a detailed description of how the inputs travel through the entity, eventually producing the outputs. The entity's block form representation in code will also be shown, along with an outline of the testing procedure. The testing was carried out using Xilinx's testbench waveform "Model Sim" Software.

Testbench waveforms of each entity are shown. A testbench will list all the inputs to the entity and the modified outputs. Also an outline of any associated problems and solutions will be detailed. Where problems and solutions are not listed it implies there were no major difficulties worth noting.

All of the following entities (except the adder/subtractor<sup>1</sup>) are entirely my own work and design. Only the required amount of bits specific to this project are used. All the code of the following descriptions can be found on the attached CD.

#### 6.2.1 Background Information

An instruction is entered in to the program, in the form of an opcode, *operation code*. Essentially this is an instruction represented in binary format. The fields of the opcode determine what is going to be computed;- what operation, on what operands,

<sup>&</sup>lt;sup>1</sup>courtesy of Morris M. Mano [4]

Figure 6.1: Top Level Schematic

and where the result will be stored.

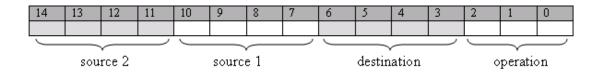

The opcode is 15 bits long, see figure: 6.2 operation  $\Rightarrow$  3 bits (0, 1, 2) source 1  $\Rightarrow$  4 bits (7, 8, 9, 10) source 2  $\Rightarrow$  4 bits (11, 12, 13, 14) destination  $\Rightarrow$  4 bits (3, 4, 5, 6)

Figure 6.2: Opcode

Slight problem - "00000000000000000000000000000000": Technically, this could be an add operation R0 + R0 = R0;

Therefore, when the opcode leaves, a validity bit has been added, making it 16 bits long. The validity bit will be 1 if the instruction is valid, and 0 if the instruction is invalid.

Entities perform a check on the instruction to evaluate whether it is valid or not. If the instruction is invalid, entities will simply disregard it and wait for a valid instruction to arrive.

#### 6.2.2 Instruction Queue

| Inputs      | Outputs |

|-------------|---------|

| clock       | opcode  |

| reset       |         |

| adder_full  |         |

| mult_full   |         |

| instruction |         |

#### **Detailed Design Description**

This entity has two functions:

- 1. To take in instructions (and store if necessary).

- 2. To output an instruction per clock cycle.

The instruction queue is organized in to a stack format, following a FIFO<sup>2</sup> queuing structure. An incoming instruction is placed in the next *lowest* available position in the stack. (e.g. if the last instruction was placed in position stack 4 - all positions above it would be free and the next instruction would be placed in stack 5). There is space for 16 instructions. See table: 6.1

| stack | 15 |

|-------|----|

| stack | 14 |

| stack | 13 |

| stack | 12 |

| stack | 11 |

| stack | 10 |

| stack | 9  |

| stack | 8  |

| stack | 7  |

| stack | 6  |

| stack | 5  |

| stack | 4  |

| stack | 3  |

| stack | 2  |

| stack | 1  |

| stack | 0  |

|       |    |

Table 6.1: Stack format implemented in VHDL entity: Instruction Queue

To *input* an instruction:

There is a 4 bit count\_pos signal (an internal variable), which identifies the next free space in the stack. It is essentially a program counter (PC). As instructions are entered, this value increments.