# Synthesisable VHDL model of a Java Virtual Machine for HAL

Louise Annamarie Reilly Supervised By: Michael Manzke B.A. (Mod.) Computer Science Final Year Project

May 2005

#### Abstract

The aim of this final year project was to implement a Java Virtual Machine on an FPGA. The FPGA is located on a hardware learning board used by second year Computer Science and third year Engineering students as part of their coursework. The introduction of a JVM to this hardware will enable students to program the FPGA with Java in place of lower level languages such as Assembly or VHDL, VHDL being the language currently in use.

This project is part of a continuing effort to upgrade the learning boards from the Motorola MC68008 microprocessor technology which has been part of the course for many years. It built upon the final year project of Ross Brennan. His project involved implementing a RISC microprocessor in place of the CISC architecture which was there and resulted in a prototype project board being designed and assembled. It was one of these boards which was used here.

The JVM implemented on the upgraded board originated as part of a PhD thesis at the Technical University of Vienna, Austria. It is an optimized JVM designed specifically for Altera software and the Cyclone board. As part of the project the original VHDL code was altered to run on Xilinx software and the Virtex-II board which the students will be working with<sup>\*†</sup>.

<sup>\*</sup>All typesetting for this report was done with LaTeX tools

<sup>&</sup>lt;sup>†</sup>All diagrams, except *Figure 4.1*, in this project were produced using Photoshop 7.0

# Contents

| 1        | Intr | oduction                                            | <b>5</b> |

|----------|------|-----------------------------------------------------|----------|

| <b>2</b> | Bac  | kground & Research                                  | 8        |

|          | 2.1  | Background of the Hardware                          | 8        |

|          | 2.2  |                                                     | 9        |

|          |      | 0                                                   | 9        |

|          |      | 2.2.2 JOP Basics                                    | 3        |

| 3        | JOI  | P Design 1                                          | 5        |

|          | 3.1  | Breaking Down The Code                              | 5        |

|          | 3.2  | The Core                                            | 5        |

|          |      | 3.2.1 Fetch component                               | 6        |

|          |      | 3.2.2 Bytecode Fetch component                      | 7        |

|          |      | 3.2.3 Decoder                                       | 7        |

|          |      | 3.2.4 Stack                                         | 7        |

|          | 3.3  | Extension                                           | 8        |

|          |      | 3.3.1 Multiplier                                    | 9        |

|          | 3.4  | IO components                                       | 0        |

|          |      | 3.4.1 Universal Asynchronous Receiver-Transmitter 2 | 1        |

|          |      | 3.4.2 Clock Counter                                 | 2        |

|          | 3.5  | External Memory                                     | 2        |

| 4        | JOI  | P Implementation 23                                 | 3        |

|          | 4.1  | Generic Parameters                                  | 3        |

|          | 4.2  | Altera Library Files                                | 4        |

|          | 4.3  | Other Methods                                       | 4        |

|          | 4.4  | Core                                                | 4        |

|          |      | 4.4.1 BCFetch                                       | 5        |

|          |      | 4.4.2 Stack                                         | 5        |

|          | 4.5  | External Memory                                     |          |

|          | 4.6  | Short RAM                                           | 6        |

|          | 4.7  | Clock Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 27        |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          | 4.8  | Top Level of Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28        |

|          | 4.9  | Pipeline Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28        |

| <b>5</b> | Har  | dware Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31        |

|          | 5.1  | Hardware Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 31        |

|          |      | 5.1.1 Configuration Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32        |

|          |      | 5.1.2 JTAG Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 32        |

|          |      | 5.1.3 Slave Serial Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34        |

|          | 5.2  | FPGAs in Detail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 34        |

|          | 5.3  | Putting the JVM onto the FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35        |

|          | 5.4  | Additional Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36        |

| 6        | Eva  | luation & Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38        |

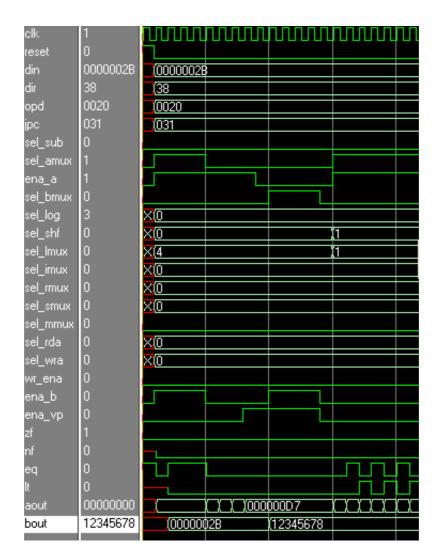

|          | 6.1  | Stack Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38        |

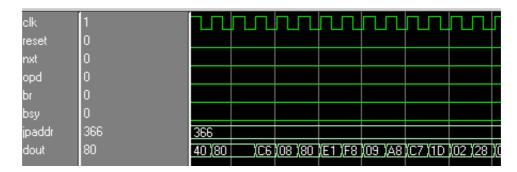

|          | 6.2  | Fetch Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40        |

|          | 6.3  | BCFetch & Decode Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40        |

|          | 6.4  | Core Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41        |

|          | 6.5  | Extension Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43        |

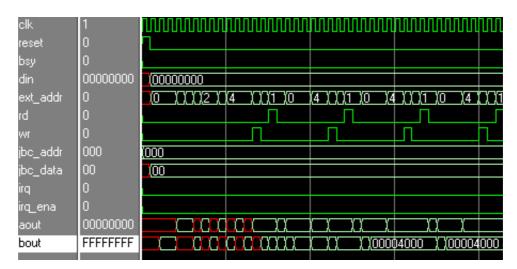

|          | 6.6  | External Memory Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44        |

|          | 6.7  | IO Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 45        |

|          | 6.8  | Set RAM Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 45        |

|          | 6.9  | 8bit RAM Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46        |

|          | 6.10 | JOP Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 48        |

| 7        | Fut  | re Work & Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49        |

| 1        | 7.1  | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>49</b> |

|          | 1.1  | 7.1.1         Class Loader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>49  |

|          |      | 7.1.2         Compiler         Compiler <t< td=""><td>49</td></t<> | 49        |

|          |      | 7.1.2         Complet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49<br>50  |

|          |      | 7.1.4 GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50<br>50  |

|          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

|          |      | Ū                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |

|          | 7.2  | 7.1.6 Threads, Interrupts and Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51<br>51  |

|          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |

| Α        | ROI  | M1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55        |

| В        | RA   | M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57        |

# List of Tables

| 3.1        | Mapping of bytecode to JVM address      | 18       |

|------------|-----------------------------------------|----------|

| 3.2        | JOP hardware registers and memory areas | 19       |

| 3.3        | Address mapping for Extension           | 20       |

| 3.4        | Operations of a Booth Multiplier        | 20       |

| 3.5        | Address mapping for IO                  | 21       |

| 3.6        | Memory mapping for External Memory      | 22       |

|            |                                         |          |

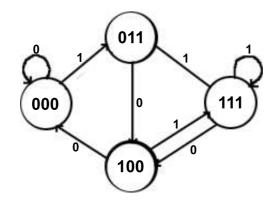

| 4.1        | Binary bits of count zero to seven      | 27       |

|            | Binary bits of count zero to seven      |          |

| 4.2        |                                         | 28       |

| 4.2<br>5.1 | 5-stage pipeline                        | 28<br>33 |

# List of Figures

| 11<br>16 |

|----------|

|          |

|          |

| 21       |

| 30       |

| 33       |

| 39       |

| 40       |

| 41       |

| 42       |

| 43       |

| 44       |

| 45       |

| 46       |

| 46       |

| 47       |

|          |

# Chapter 1

# Introduction

Throughout the course of this report, it is hoped that the reader will gain a firm understanding of the methods required to:

- 1. Create a Java Virtual Machine.

- 2. Implement a Java Virtual Machine on a microprocessor.

- 3. Run programs on an FPGA.

- 4. Port VHDL code from Altera to Xilinx.

- 5. Test VHDL code.

These five processes will be covered in detail in the coming chapters.

This project set out originally to implement VHDL code for a JVM<sup>\*</sup> on a piece of available hardware referred to as the HAL<sup>†</sup>. It builds upon the work of Ross Brennan two years ago, which began the HAL project.

There is always a need to expand knowledge and to ascertain what is possible. This project is a good representation of this, being a research one. It tests the boundaries of an FPGA<sup>‡</sup> on board the HAL. At the beginning of it, no-one was even certain if placing a JVM on the hardware board was possible. Much time was expended researching similar projects as well as working on the JVM at hand.

The HAL project is currently trying to have several CPUs on the one board. The FPGA is easily configurable and can be reprogrammed in very little time. Therefore it has the potential to run several different functions

<sup>\*</sup>Java Virtual Machine

<sup>&</sup>lt;sup>†</sup>Hardware and Architecture Lab-board

<sup>&</sup>lt;sup>‡</sup>Field Programmable Gate Array

and have many different CPUs all providing different operations and modes of use. There are several projects which could span from Ross', it has opened the door to many new possibilities. Putting a Java platform on the board is just one of these possibilities and has been attempted in this project.

The HAL (Chapter 2) is a learning board for Engineering and Computer Science students of Trinity College Dublin. The boards which currently make up part of the Trinity courses are different to the one used in this project. The older boards draw upon technology from the early 80's and are now almost totally obsolete. It is hoped that they will be changed over to the new HAL boards. The HAL board is a Virtex II Prototype Platform board which was altered by Ross Brennan in his Final Year Project[3] to replace the older boards.

The major problem faced when undergoing such a project as this is lack of knowledge. Chapter 2 not only details the hardware board utilised in this project, it also covers a lot of the research done to try to gain a firm grasp of what is involved in implementing a JVM written for a different hardware board on the available one. A synopsis of the research involved in this project is included in this chapter. It will go through the basics of JVMs in general and the JOP<sup>§</sup>, Martin Schoeberl's version of the JVM[14], in particular. The background of the VHDL code which produces the JVM is gone through here. This code was downloaded from Schoeberl's website. Much time was spent reading through documentation on this website as well as that of other sources.

Chapter 3 covers the original VHDL code downloaded from Schoeberl's site[14]. The code has been split modularly to better explain what each section does. Having analysed each integral code segment their interactions with each other are examined. This will provide the reader with a clear picture in their mind of how the JOP was originally written and how JVMs generally interact with each other. In doing this the reader is provided with the necessary prerequisite knowledge of the JOP and an understanding of the foundation on which the project has been based.

The alteration of the design and subsequently coded implementation is detailed in Chapter 4. The code had to be ported from Altera on Cyclone boards to Xilinx running on Virtex II boards as the original software and hardware platforms were unavailable for this project. In addition, several sections of new code had to be introduced which necessitated fundamental changes to the circuit design and subsequently its component interactions. This chapter will go over such changes and shows much of the work undertaken.

<sup>&</sup>lt;sup>§</sup>Java Optimized Processor

Chapter 5 gives physical details of the HAL. Included in this chapter is a full description of the layout of the board and its different modes of operation. This chapter will go into detail on how to use the board and there is a summary of everything needed to program the HAL with VHDL code. This was a significant component in the final stage of this project and would ultimately provide proof of concept. As such great care was taken in the correct operation of the software and hardware involved in coding and testing. This is where the completed JVM would run. The following two chapters will cover all of the elements of this stage in the project with the latter describing the testing which was required on the board.

Chapter 6 describes what was involved in the overall testing and evaluation. The code was tested extensively with ModelSim simulation tools before finally being loaded onto the board and tested there. Each component of the JOP had to be tested. The evaluation was an ongoing process and as such was dispersed throughout the duration of this project. At every point, from first downloading the code, to getting it onto the board, there were tests carried out to ensure that everything was operating as it should be. The testing finally ended when the JOP was running correctly on the board and, as such, this chapter completes the implementation process of the JOP. After reading these chapters the reader should have a firm grasp of the different processes undertaken to complete this project.

Chapter 7 suggests several avenues which may be pursued as a continuation of this project. In this chapter the reader will find several areas where the study of JOP in this environment can be built on. There are feature recommendations as well as full projects which could spawn from the work to date and the chapter covers a few of the possibilities.

# Chapter 2

# Background & Research

### 2.1 Background of the Hardware

As has already been mentioned, this project builds upon work done by Ross Brennan[3] two years previously for his final year project. His project involved replacing the MC68008 microprocessor with a LEON2-1.0.10-xst\* SPARC-V8 processor implemented on an FPGA. The LEON processor was freely released under the GNU-LGPL license and is available for download from the Internet.

In the process of testing the new processor, Ross designed two boards capable of running and using it. He used the Virtex II prototyping and design boards available from Xilinx. On these he connected various chips, including an Atmel AT29LV020 ROM, an ISSI IS63LV1024L RAM and a Maxim-IC MAX3232CPE IO chip. Currently, it is hoped that these boards may eventually be capable of running several different CPUs. This project, Ross', and several others are being attempted towards this end.

The original MC68008 boards were used as teaching aids for second year Computer Science and third year Engineering students in Trinity College Dublin. The students are able to get a hands-on feel for microprocessor design by wiring up the MC68008 boards, connecting the microprocessor to external chips, and programming them. The microprocessors on these boards are programmable using Assembly language and are implemented using CISC<sup>†</sup> architecture. Though still a worthwhile exercise, these boards are by now severely outdated and in need of upgrading. Hence the use of final year projects, such as Ross' and mine, to find a newer solution than the MC68008.

<sup>\*</sup>available from http://www.gaisler.com

<sup>&</sup>lt;sup>†</sup>Complex Instruction Set Computer

The LEON core is an example of a RISC<sup>‡</sup> architecture. Chips designed using RISC architecture are cheaper to design and run quicker than those implemented in CISC. CISC use more complex instructions, these can be slow and time consuming on a processor. On the other hand, RISC have relatively few instructions, and those it does have are kept simple and brief, making them quicker to run. This makes RISC, in places, more advantageous than CISC.

One of these places is on the learning boards. The students use these boards to get an insight into architecture design. They concentrate more on the hardware than the software implemented on the boards and don't need as many instructions.

### 2.2 Background of the Software

The original code for the JVM was downloaded as open source code from http://www.jopdesign.com[14]. This site holds work and documentation completed by Martin Schoeberl as part of his PhD. thesis in the Technical University of Vienna, Austria. He set out to develop a simple Java processor which was optimized down so that it only executes Java bytecode[14]. He called his hardware implementation of this processor JOP.

#### 2.2.1 JVM Basics

The Java Virtual Machine allows a Java program to be run on any hardware. Many programming languages are written to be run on a particular Operating System. Java however, was released as an integrated language for the Netscape Internet browser[14]. This meant that at any given time it could be run on any Operating System. Java needed to be portable.

The JVM provides this portability. A JVM resides on the hardware, it interacts with the OS in native code belonging to that system. Any Java programs trying to run on the OS must work through the JVM. It is the Java translator.

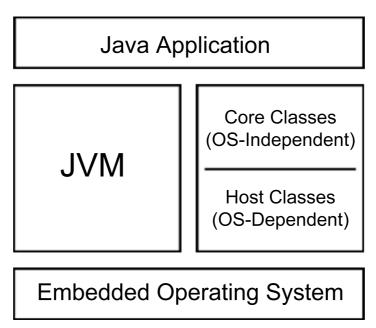

The JVM can be split up into several different layers, as shown in *Figure* 2.1[13]. The uppermost layer is the part which the programmer or user interacts with. It holds the actual Java Application and generally comes in the form of an editor or compiler, or both, which the JVM provides. The programmer puts his/her code into this upper layer and compiles it.

When the program is compiled, a .class file is created. These .class files contain:

<sup>&</sup>lt;sup>‡</sup>Reduced Instruction Set Computer

- 1. Virtual machine code for methods of the Java class.

- 2. Symbolic reference to the upper levels of the Java class.

- 3. List of fields defined by the Java class.

- 4. Literals and symbols used by the Java class.

- 5. Other data required by the Java runtime system.

What this boils down to is that the .class file contains bytecode[6]. The original code is broken down and translated to this. Bytecode is an intermediate code which exists between the source and machine code[9]. The bytecode encodes the above list, the JVM then translates the .class file to a .exe<sup>§</sup> file[6], and runs it on the lower down Operating System, thus providing Java with much of its portability and basically acting as a translator or a go-between.

Figure 2.1: JVM Platform

The JVM translates the bytecode to machine code, specific to whichever machine the JVM currently rests on, or rather, the JVM interacts between classes from the Java Application and those residing in the Operating System. It provides bytecode which is an intermediate language between them and

<sup>&</sup>lt;sup>§</sup>Executable

acts as a medium, thereby running the Java classes on whatever hardware is available.

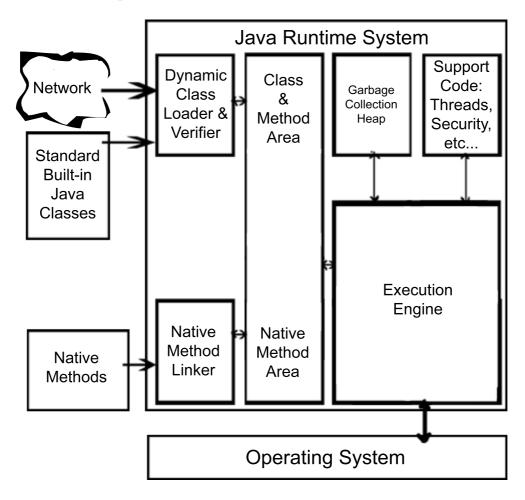

Figure 2.2 shows a more in-depth view of the components of a basic JVM[9]. This figure can be related to the previous one, but provides greater detail of the components and how the JVM works.

Figure 2.2: JVM Components

The Java Runtime System is the JVM.

The Execution Engine is the equivalent of a virtual processor[9]. It receives a stream of bytecode and executes instructions contained therein. It interacts directly with most of the JVM as well as with the Operating System.

Native Method Support enables calling of methods from the underlying code in different languages. It is the translator from bytecode to machine code and is hardware specific. Referring to *Figure 2.1*, it is the link between the core and the host classes. The native methods are those belonging to the

OS, generally C/C++. The JVM associates these with the bytecode instructions contained in the Execution Engine and thus translates the bytecode to its corresponding native method, ie: creating a .exe file, and sends them to the Operating System.

The Class Loader dynamically loads Java classes from the Java class files[9]. These files can come from Java Library files or from the programmer. The Class Loader quickly runs through and verifies the code, preparing the files for execution.

The Class and Method Area holds necessary bytecode for programs. It has areas for both native methods and Java classes, feeding both through to the Execution Engine as they are needed.

The Garbage Collection Heap reclaims system resources when the code has finished using them[13]. It simplifies programming, helping to avoid such classic errors as memory leaks.

Support Code controls threads, interrupts, exceptions, etc. Threads and scheduling tools in Java have very loosely defined rules. For example, a lower priority thread can preempt a higher priority one. This does help prevent starvation but unfortunately is unacceptable in a JVM due to the importance of interrupts to a real-time system. The support code helps alter this behaviour[14].

The JVM simply acts as a platform between the Java program and the Native Methods of the Operating System. JVMs are OS specific, their lower layers interacting directly with the OS. Their upper levels however, can run any Java software. Therefore, a program written on a Mac, could be transported to a machine running Linux, and from there to one running Windows with no problems. This is because the Java program would not have to change at all to compile on the JVM on the system. The system JVM would act as a cushion between the program and the OS, translating easily from source to machine code for any of the machines and any Operating System.

#### Other JVMs

There are several other JVMs available. During the research section of this project, many were looked at. They provided a wider perspective of the project and how it can be implemented, as well as an insight into the amount of work required to get even the basic features working.

One such was *kissme*. *Kissme* is freely available under the  $\text{GNU}^{\P}$   $\text{GPL}^{\parallel}$ . It was an Honours project by Stephen Tjasink in the University of Cape Town, South Africa. It was developed for a set-top box that came with a TV

<sup>¶</sup>GNU's Not UNIX

General Public License

Satellite Decoder. The JVM was run on a slow processor and class files had to be stored in the ROM, similar to the JOP. This project was continued as part of Stephen Tjasink's Masters degree to support more advanced features such as persistent programming[7].

*Kissme* works on UNIX systems and can run console Java applications. It is written in C, Assembly and Java. It currently has native threads, garbage collection and uses GNU classpath libraries. It supports an extension for orthogonal persistence which will transport Java data structures between memory and a persistent store, a feature added as part of Tjasink's Masters degree. Also in development is a Just-In-Time compiler for it named *cavalry* which is written in Java. *Kissme* is still a work in progress.

#### 2.2.2 JOP Basics

The JOP forgoes all of the upper levels of the JVM, running it right down to the basics. This optimized JVM must have an external compiler and editor to create a .class file. It doesn't have a dynamic Class Loader so the .class file, for this implementation at least, must be placed in a predefined static location, ie: the ROM, where the JOP can access it.

Once the JOP has the bytecode, it acts in a similar manner to the JVM. It has the equivalent of an Execution Engine which translates the bytecode to hardware specific code and runs the commands necessary to execute this code before translating the results back. All the code for this resides in the Core of the JOP (Section 3.2). The results are saved and would require an external application to translate them to a human readable or usable format.

Future work for this project will be discussed in Chapter 7. External applications mentioned here could be created and tied in with the work done on the JOP so far. Making specific applications for this would remove unnecessary reliance on external software.

To optimize further, the Support Code has also been removed, or rather, been moved closer to the Execution Engine. The JOP has been stripped to its bare bones essentials discarding superfluous methods such as the ability to manipulate multiple threaded environments.

The JOP is already so well optimized in its internals that it was decided to abolish the Garbage Collection Heap. Due to limitations of the instruction set, and the existence memory reclamation code in each segment of the JOP, the Garbage Collection Heap became redundant and thus provided an opportunity to free up much needed microcontroller space.

The preceding optimisations shrink the already small JVM to such an extent that it will comfortably operate on an FPGA microprocessor having come from an ample PC environment. The RISC architecture on the Virtex II

boards makes programming them an arduous task. The reduced instructions means that the microprocessor is now only programmable with a limited set of languages. These languages are only one or two steps removed from actual machine code and contain very simple instructions. Having a JVM implemented on these chips will provide more functionality and usability than that available with RISC architecture.

# Chapter 3

# JOP Design

### 3.1 Breaking Down The Code

The original code was downloaded directly from Michael Schoeberl's website[14]. It had to be split up, broken down and understood. The line count of the original code plus libraries from Altera[2] and the IEEE[5] totals 11,130 lines. The final line count totalled a mere 4,575 lines, much less than half of the original count.

The original code was analysed and described using pseudo code to better understand the application flow and module interactions and dependencies. This translation afforded a simplified overview of the entire code structure allowing easy manipulation of the comprising elements. Areas which were at this time incomprehensible could then be identified, isolated and studied autonomously.

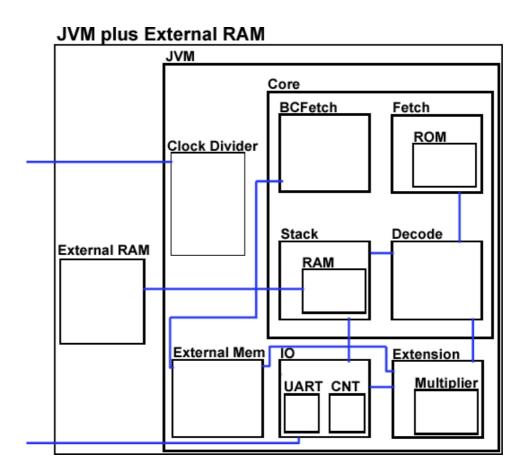

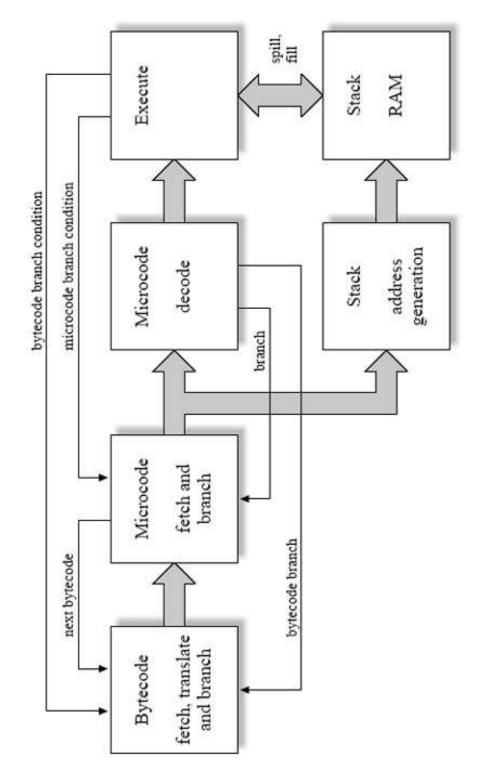

The next logical step undertaken was a more specific overview of the program as a whole. This in turn lead to the view of components shown in *Figure 3.1* as well as a detailed observation of how they interact.

The following sections describe the original design and code implementation. Subsequent alterations and additional components which were a direct result of this project will be detailed in Chapter 4.

### 3.2 The Core

The Core component encapsulates much of the memory, Stack and ALU functions. It gives the JVM much of its functionality and can also be split into sections for better understanding.

Figure 3.1: Components of the JVM

#### 3.2.1 Fetch component

The Fetch component works with the ROM, feeding bytecode instructions from the ROM directly to the Decoder where they will be translated to JVM addresses. Bytecode was explained in Section 2.2.1

Data in the ROM is 10bits long and contains bytecode. As mentioned previously, bytecode is created when a Java program is compiled and is an intermediate layer of code between source and machine code[9]. It is stored into the ROM and is accessed by Fetch. From Fetch it is sent, via the core, to the Decoder where the bytecode will be split into instructions.

A segment of the ROM code is located in Appendix A. The entire code, too long to include here, is located on the disk provided with this report.

#### **3.2.2** Bytecode Fetch component

In the Bytecode Fetch part of the JVM, *jump* and *branch* instructions are decoded and flags are set so that they can be recognised and executed when they reach the stack. The signals *busy* and *branch* are then sent back to Fetch to stop other instructions getting through, in the case of an interrupt, or to change the memory address of the next instruction, in the case of a branch.

#### 3.2.3 Decoder

Here the bytecode is input from Fetch and translated to a JVM address. The mappings for the instructions are shown in *Table 3.1*.

These instructions show the importance of the Stack. Explanations of all the above instructions are available in *timing.pdf* on the JOP[14] website. *Table 3.2* has been reproduced here based directly on Martin Schoeberl's work and explains the registers and memory areas used by the optimized JVM. Additional information is available from *timing.pdf* in which pages 11 to 33 provide a full explanation of all of the above instructions.

#### 3.2.4 Stack

JVMs are stack based. The stack is split into three main sections: one section holds local variables, another exists as the execution environment and the last holds the operand stack. The execution environment maintains the current operations of the stack and the operand stack is a workspace for bytecode instructions and parameters[15].

The Stack component does not just implement the typical push and pop instructions. This component is an overlay on the three sections of the stack mentioned above and as such it can also perform all the logic and arithmetic methods for the system, working on the JVM addresses sent to it by the decoder. The original Stack held a 32bit RAM, alterations had to made to this and will be detailed in the next chapter.

Most of the RAM is filled with the hexadecimal value &H12345678<sup>\*</sup>. However, there are some constants sent in. The values of the RAM file are located in Appendix B.

<sup>\*</sup>Throughout this report, whenever &H is used it is prefixing a hexadecimal value

| Bytecode         | Instruction            | Bytecode         | Instruction |  |

|------------------|------------------------|------------------|-------------|--|

| (in hexadecimal) |                        | (in hexadecimal) |             |  |

| 00               | pop                    | pop 2X/3X        |             |  |

| 01               | and                    | 4X/5X            | bz          |  |

| 02               | or                     | 6X/7X            | bnz         |  |

| 03               | xor                    | 80               | nop         |  |

| 04               | add                    | 82               | jbr         |  |

| 05               | $\operatorname{sub}$   | aX/bX            | ldm         |  |

| 08               | stioa                  | cX/dX            | ldi         |  |

| 09               | stiod                  | e1               | ldiod       |  |

| 0a               | stmra                  | e2               | ldmrd       |  |

| 0b               | stmwa                  | e3               | ldmbsy      |  |

| 0c               | stmwd                  | e5               | ldmul       |  |

| 0d               | stopa                  | e8               | ld0         |  |

| 0e               | $\operatorname{stopb}$ | e9               | ld1         |  |

| 10               | $\mathrm{st0}$         | ea               | ld2         |  |

| 11               | $\mathrm{st1}$         | eb               | ld3         |  |

| 12               | st2                    | ed               | ld          |  |

| 13               | st3                    | fO               | ldsp        |  |

| 15               | $\operatorname{st}$    | f1               | ldvp        |  |

| 18               | $\operatorname{stvp}$  | f2               | ldjpc       |  |

| 19               | $\operatorname{stjpc}$ | f4               | ld_opd_8u   |  |

| 1a               | not used               | f5               | lp_opd_8s   |  |

| 1b               | $\operatorname{stsp}$  | f6               | ld_opd_16u  |  |

| 1c               | ushr                   | f7               | ld_opd_16s  |  |

| 1d               | shl                    | f8               | dup         |  |

| 1e               | $\operatorname{shr}$   |                  |             |  |

Table 3.1: Mapping of bytecode to JVM address

# 3.3 Extension

Extension provides an interface between External Memory, IO, a Multiplier and the Core, mapping each to the other. Depending on signals coming from the Core it schedules reading and writing from each of these components. The address mapping is shown in *Table 3.3*, the address coming from the Core where it was encoded with the bytecode coming from the RAM and translated in the Decoder before being passed on to this external component. Some addresses are duplicated in the table because they will be sending

| Name       | Description                                    |  |  |

|------------|------------------------------------------------|--|--|

| A          | Top of the stack                               |  |  |

| В          | The element one below the top of stack         |  |  |

| stack[]    | The stack buffer for the rest of the stack     |  |  |

| sp         | The stack pointer for the stack buffer         |  |  |

| vp         | The variable pointer. Points to the first      |  |  |

|            | local variable in the stack buffer             |  |  |

| pc         | Microcode program counter                      |  |  |

| offtbl     | Table for branch offsets                       |  |  |

| jpc        | Program counter for the Java bytecode          |  |  |

| opd        | 8 bit operand from the bytecode fetch unit     |  |  |

| ioar       | Address register of the IO subsystem           |  |  |

| memrda     | Read address register of the memory subsystem  |  |  |

| memwra     | Write address register of the memory subsystem |  |  |

| memrdd     | Read data register of the memory subsystem     |  |  |

| memwrd     | Write data register of the memory subsystem    |  |  |

| mula, mulb | Operands of the hardware multiplier            |  |  |

| mulr       | Result register of the hardware multiplier     |  |  |

| member     | Bytecode address and length register           |  |  |

|            | of the memory subsystem                        |  |  |

Table 3.2: JOP hardware registers and memory areas

instructions to multiple components.

#### 3.3.1 Multiplier

The Multiplier implemented in Extension uses the Booth Algorithm. Each computation takes as many clock cycles as there are bits in the multiplicands. Here the multiplicands are all 32bits long so every multiplication takes 32 clock cycles.