In the Name of God, the Compassionate, the Merciful

# Open Source Real-Time OS (RTEMS) on SCI based Compute Clusters

# Salman Taherian

Senior Sophister Final Year Project Supervisor: Michael Manzke

B.A.I. Bachelor in Engineering &B.A. Bachelor in Arts

University of Dublin

Trinity College

School of Engineering

2003

## University of Dublin

#### Abstract

# Open Source Real-Time OS (RTEMS) on SCI based Compute Clusters

A new class of real-time application demanding high computation and parallel processing power has begin to emerge. It is believed that previously proven successful compute clusters could once again, offer an optimum and cost-effective solution to such demand. This project investigates the implementation of a specific real-time compute cluster (RTCC). A dedicated cluster interconnect, SCI (Scalable Coherent Interface) - *IEEE Approved Standard 1596-1992*, with hardware based functionality and deterministic performance was selected as the RTCC interconnect. Implementation focuses primarily on the hardware based distributed shared memory (DSM) offered by the SCI technology as the basis of inter-communication within the RTCC; while providing a solid platform for support of future SCI functionalities on the RTCC.

RTEMS, Real-Time Executive for Multiprocessor Systems - an "open source", "licence free", real-time dedicated operating system, was evaluated as the target real-time operating system performing on the RTCC. This project investigates the incorporation of SCI technology in RTEMS (supporting SCI functionalities and drivers), as well as implementation of a suitable real-time cluster computing library on RTEMS for support of DSM based RTCC. Finally, this project presents a mechanism of performing real-time computing by utilising the DSM based intercommunication. Synchronisation and mutual exclusion facilities are also supported through implementation of a suitable two stage lock mechanism.

# ACKNOWLEDGMENTS

First and foremost I would like to thank my family, especially my parents for all their help and support throughout this year, not forgetting the past twenty. My supervisor, Michael Manzke, merits great appreciation for his advice, support and guidance on all aspects of this project.

I would also like to thank the RTEMS developers and the people on the RTEMS mailing list, particularly Joel Sherrill - Director of Research & Development of OAR Corporation, Ralf Corsepius for and Gregory Menke for their support and guidance throughout this project. Hugo Kohmann, from Dolphin Interconnect Solutions Inc., also merits special thanks for helping me to achieve an in-depth realisation, implementation and understanding of the SCI technology.

Finally, I would like to thank Sean McEvoy for his guidance on project, time and risk management in projects, which proved beneficial and Nichola Murphy for proof-reading the project report and presenting her useful comments.

# TABLE OF CONTENTS

| List of       | Figures                                        | iv |

|---------------|------------------------------------------------|----|

| ${f List}$ of | Tables                                         | v  |

| Glossa        | ry                                             | vi |

| Chapte        | er 1: Introduction                             | 1  |

| Chapte        | er 2: Compute Clusters & Cluster Interconnects | 5  |

| 2.1           | Clusters                                       | 5  |

| 2.2           | Scalable Coherent Interface                    | 7  |

| Chapte        | er 3: Real-Time Operating Systems              | 15 |

| 3.1           | Hard Real-Time Systems                         | 17 |

| 3.2           | Soft Real-Time Systems                         | 18 |

| 3.3           | Real-Time Kernels                              | 18 |

| Chapte        | er 4: SCI Drivers                              | 21 |

| 4.1           | Drivers                                        | 22 |

| 4.2           | Drivers on Linux                               | 22 |

| 4.3           | Drivers on VxWorks                             | 25 |

| 4.4           | Structure of SCI Drivers                       | 29 |

| 4.5           | Compilation, Build & Configuration             | 31 |

| 4.6           | IRM                                            | 32 |

| 47            | SISCI                                          | 39 |

| Chapte  | er 5: RTEMS                                                 | <b>42</b> |

|---------|-------------------------------------------------------------|-----------|

| 5.1     | RTEMS Rate Monotonic Scheduling (RMS)                       | 43        |

| 5.2     | Comparison of RTEMS with others                             | 44        |

| 5.3     | RTEMS Structure                                             | 50        |

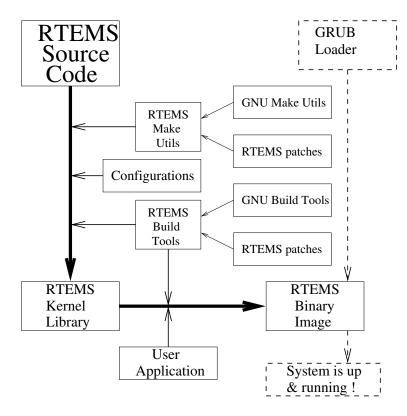

| 5.4     | RTEMS Build                                                 | 52        |

| 5.5     | RTEMS Initialisation                                        | 57        |

| 5.6     | RTEMS Device Drivers                                        | 59        |

| 5.7     | Comparison of Device Drivers on RTEMS, VxWorks and Linux $$ | 61        |

| Chapte  | er 6: Implementation                                        | 63        |

| 6.1     | SCI drivers on RTEMS                                        | 64        |

| 6.2     | Building drivers under RTEMS                                | 65        |

| 6.3     | SCI Initialisation within BSP                               | 67        |

| 6.4     | SCI driver development on RTEMS                             | 71        |

| 6.5     | Application layer                                           | 79        |

| 6.6     | Debugging                                                   | 83        |

| 6.7     | SISCI layer                                                 | 84        |

| Chapte  | er 7: Evaluation & Conclusion                               | 87        |

| 7.1     | Implementation                                              | 87        |

| 7.2     | Project                                                     | 88        |

| 7.3     | Future work                                                 | 90        |

| Bibliog | graphy                                                      | 92        |

| Appen   | dix A: RTCC Package API                                     | 96        |

| A.1     | SCI Initialisation Library (sci_init.h)                     | 96        |

| A.2     | SCI Driver Interface (sci_genif.h)                          | 97        |

| A.3     | Real-Time Cluster Computing Library (librtcc.h)             | 97        |

| Appen | dix B: Discovered GCC bug   | 99  |

|-------|-----------------------------|-----|

| B.1   | Symptom                     | 99  |

| B.2   | Cause                       | 99  |

| B.3   | Workaround                  | 100 |

| B.4   | Resolution                  | 100 |

| B.5   | Status                      | 100 |

| Appen | dix C: Concepts & Tools     | 101 |

| C.1   | Technical Concepts learnt   | 101 |

| C.2   | Tools and Software utilised | 101 |

# LIST OF FIGURES

| 2.1 | Distributed Shared Memory diagram                | 10 |

|-----|--------------------------------------------------|----|

| 2.2 | PCI-SCI card overview                            | 12 |

| 2.3 | SCI Link Controller chip overview                | 13 |

|     |                                                  |    |

| 4.1 | Linux Module-Kernel Inter-communications Diagram | 24 |

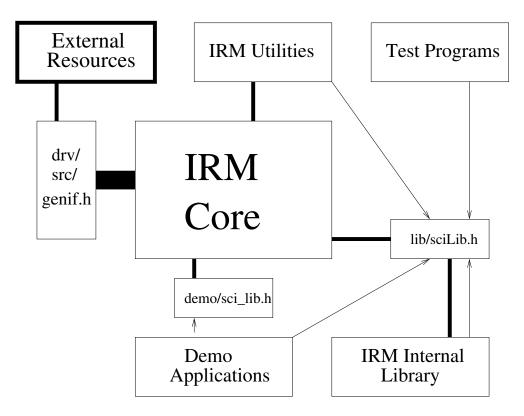

| 4.2 | IRM Internal Structure Diagram                   | 30 |

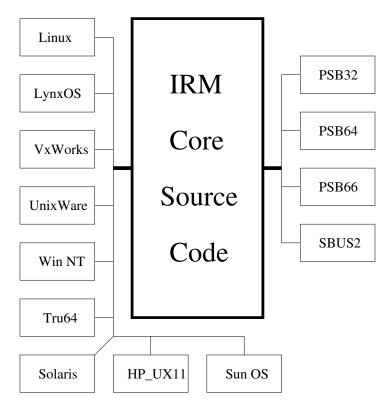

| 4.3 | IRM Source Code Overview                         | 33 |

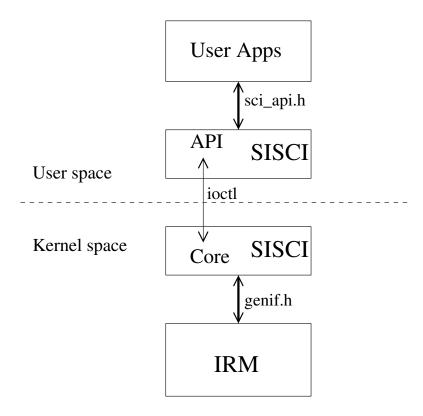

| 4.4 | SISCI Source Code Overview                       | 40 |

|     |                                                  |    |

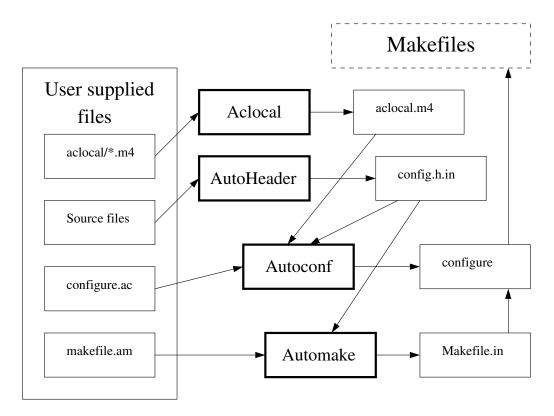

| 5.1 | RTEMS build diagram                              | 53 |

| 5.2 | RTEMS Makefiles                                  | 55 |

|     |                                                  |    |

| 6.1 | SCI Shared Memory Segment                        | 80 |

# LIST OF TABLES

| 5.1 | RTOS's Features List       |  |  |  |  |  |  |  |  |  |  |  | 46 |

|-----|----------------------------|--|--|--|--|--|--|--|--|--|--|--|----|

| 5.2 | RTOS's Latency comparisons |  |  |  |  |  |  |  |  |  |  |  | 47 |

# **GLOSSARY**

- **API** Application Programming Interface, hides low programming detail and provides a unique interface for higher level applications.

- **ATC** Address Translation Cache, internal SCI cache for mapping PCI and SCI addresses.

- **ATT** Address Translation Table, used on SCI card to translate PCI addresses to SCI addresses and vice versa.

- **BSP** Board Support Package, all portions of RTEMS which are board specific.

- **BWCE** Burst Write Combining Enable, an advanced PCI bus feature on HB\_450NX\_PXB host-bridges.

- Context Switching Delay The time delay from the execution of the last instruction of a task, to execution of the first instruction of another task, which includes the time scheduler determines which task to run, time to save the context of first task and time to restore the context of the second task.

- **DSM** Distributed Shared Memory, memory segment accessible by all cluster nodes at hardware level.

- **FAA** Federal Aviation Administration.

- **HAC** High Availability Computing

- **HPC** High Performance Computing

- **HTC** High Throughput Computing

Interrupt Latency The time elapsed from the moment of occurrence of an event (e.g. a hardware interrupt) until execution of the first instruction of the Interrupt Service Routine (ISR), which includes the overhead required by the executive at the beginning of each ISR plus the time required for the CPU to vector the interrupt.

**IRM** Interconnect Resource Manager, main section of SCI drivers which directly interacts with SCI hardware.

IRQ Interrupt ReQuest, the number of interrupt levels available within a system.

**ISR** Interrupt Service Routine, also known as Interrupt handler.

**IT** Information Technology.

LC Link Controller, interfaces the SCI card to the global SCI network.

**LIBRTCC** Real-time cluster computing library, supports real-time computing on a RTCC.

MMU Memory Management Unit.

**OS** Operating System, controls and provides a unique hardware independent interface for user applications to access hardware.

**PIO** Programmed I/O, capability of executing load and store instruction on remote cluster nodes.

**PSB** PCI-SCI Bridge, interfaces the PCI bus to the SCI card.

**RMS** Rate Monotonic Scheduling, special scheduling algorithm utilised in RTEMS to schedule periodic real-time tasks.

**ROM** Read-Only Memory.

RTC Real Time Clock, utilities in sensitive embedded applications to perform execution on high accurate basis.

RTCC Real-Time Compute Cluster.

**RTEMS** Real-Time Executive for Multiprocessor Systems, the RTOS used within this project.

**RTOS** Real-Time Operating System.

**SCI** Scalable Coherent Interface, IEEE standard interface technology, dedicated as cluster interconnects.

**SMP** Symmetric Multi-Processor, several processors on a single bus, forming a supercomputer.

VC Virtual Channel, forms the second layer of the SCI inter-communications protocol.

# Chapter 1

# INTRODUCTION

Not long ago, substantial computing power was only available within supercomputers. These high-performance systems have always been very expensive due to high design costs and the relatively small market for them. Today however, powerful computer clusters can be built for a fraction of the cost of traditional supercomputers by combining inexpensive, mass-produced PCs with dedicated cluster interconnects.

Clusters are known to have two significant characteristics: (i) They are a costeffective alternative to large scale parallel systems and (ii) They are scalable. The

most vital component in a cluster is the *interconnect*, which connects separate computer nodes to form a "unified computing resource" [1]. Communication latency,

throughput and scalability are important parameters when building a cluster of

interconnected computers. These parameters are all governed by the cluster interconnect, which is utilised in the formation of the cluster. The importance of

interconnects in a cluster was recognised, hence Dolphin PCI-SCI (D310 model)

interconnect cards were adapted for this project. This interconnect, referred to as

SCI (Scalable Coherent Interface), is an implementation of the *IEEE*, *SCI*: Scalable

Coherent Interface, Approved Standard 1596-1992. SCI is a dedicated cluster interconnect, implemented specifically for the task of constructing clusters from a series

of standalone computers [29].

Parallel computing may be divided into two classes: Moderate Parallel systems based on shared memory (typical SMP machines) and Highly Parallel machines based on message passing. SCI offers low latency message passing through non-cached shared memory. Remote memory read, write, lock, interrupt and DMA operations are available. Hence, SCI cards for a standard PCI bus offer both low

latency message passing and distributed shared memory with a large number of processing nodes for a moderate price. Even though sources of performance loss within clusters are the slow PCI bus and the SCI link latency, advancements within the SCI technology have shifted the focus of the performance loss purely on to the PCI bus.

Another class of systems, which are fast emerging into the IT<sup>1</sup> industry, are the *Real-Time* systems. Real-time systems are classified as systems which possess timing constraints on their execution. These constraints require the system to operate in a predictable and deterministic fashion. Real-time systems are widely used within embedded applications, where systems are task or operation specific and in most cases required to be fully reliable. Growth of computer system applications in all areas, together with the merging of old multi-media systems and modern computer systems, has increased the demand in real-time systems more than any other previous time.

Modern real-time systems increasingly demand higher computational power. This may be clearly seen within the developing network and communication technologies (3G, 4G, etc), which are required to support a tremendously large amount of network load on a real-time basis. While real-time based supercomputers may be utilised under such circumstances, this project investigates provision of a cost-effective solution, RTCC (Real-Time Compute Cluster). There have already been a number of attempts in implementation of the RTCC, but these have either been based on proprietary systems or they lack the high-performance required.

The RTOS (Real-Time Operating System) chosen for this project is an open source, real-time and embedded dedicated operating system named RTEMS. RTEMS, Real-Time Executive for Multiprocessor Systems, is a "licence free" operating system with an extensive set of features and a performance comparable with the most successful real-time operating systems in the industry (e.g. VxWorks). This project evaluates RTEMS on an SCI based compute cluster in order to achieve an inexpensive high-performance RTCC. The following points are considered noteworthy when

<sup>&</sup>lt;sup>1</sup>Information Technology

analysing the choice of elements within this project.

- RTEMS is a high performance RTOS, and SCI a dedicated cluster interconnect with a sufficiently high performance, they are hoped to contribute towards a high-performance RTCC.

- RTEMS is an "open source" and "licence free" system and thus not only significantly reduces the cost when compared to expensive proprietary systems, but it also offers future research and development possibilities in this area.

- Inexpensive D310 model PCI-SCI cards, which offer the required distributed shared memory capability were adapted for this project. They also represent a hardware based, deterministic behaviour, most suitable for real-time systems.

This project will initially aim at incorporating SCI compatibility into the RTEMS system. Analysis of SCI hardware and specifically SCI drivers, as well as RTOS's and specifically RTEMS system, were of extreme importance in this section. It was necessary to implement full functionality of the SCI hardware on RTEMS, without introducing any disadvantages or performance losses into the overall system. SCI technology has particularly close ties with the memory management of systems, which need extra attention. In addition, SCI drivers and operations must comply with requirement and standards of a real-time system. Efforts were made to implement SCI functionality on RTEMS most efficiently and in-line with other sections of the system. The second section of this project is dedicated to the implementation of the hardware based DSM (Distributed Shared Memory) within a cluster. Following this section a full RTCC is implemented with DSM as a basis for cluster inter-communications. In the final stage of this project, a two stage lock mechanism is developed to support inter-process synchronisation within a cluster, along with a simple demonstration program illustrating the result of project on a two node computer cluster.

This report is composed of seven chapters and three appendices. The following two chapters provide background information regarding clusters, SCI and RTOS in general. Chapters four and five examine in detail, the SCI driver and RTEMS, respectively. Lack of documentation in many cases, particularly the SCI drivers, encourages us to present a detailed view of overall elements examined. It is further hoped that this project report will serve as an implementation guide and/or documentation for systems examined throughout this project. Chapter six details the implementation of the RTCC and analysis the implementation from various perspectives. Finally, chapter seven presents results of the implementation along with conclusions and an overall evaluation of this project.

# Chapter 2

#### COMPUTE CLUSTERS & CLUSTER INTERCONNECTS

The wide spread use of digital technology and particularly computers within our daily lives has augmented the need for higher computation power within systems. In response to this demand hardware manufacturers are producing newer and faster hardware (and more specifically processors), on monthly basis. It is the high demand for computation power which contributes towards the rapid advancement of the computer technology. Unfortunately, there is a cost associated with this rapid advancement. As the technology becomes more advanced and complex, the cost of production and the related cost of purchase elevates.

Continuously maintaining supercomputers and mainframes to the highest level of technology is extremely costly and in most cases, uneconomical. The concept of a compute cluster offers construction of cheap supercomputers with the option of performance scaling, which is independent of technology development, and with minimum additional costs. Mentioned factors have resulted in rapid deployment of compute clusters within various industrial sectors, and in particular the replacement of high performance and large scale supercomputers with the more promising compute clusters. This chapter will provide a brief introduction to the significance of compute clusters, followed by a detailed examination of the interconnects employed within clusters. This project specifically employs SCI (Scalable Coherent Interface) interconnects manufactured by Dolphin. Hence the second section of this chapter will be focus entirely on this hardware and technology.

#### 2.1 Clusters

A cluster is a collection of interconnected whole computers used as a single unified computer. Traditionally, parts of computer systems and mainframes had to be replaced with new hardware if higher computation or processing power was desired. Due to compatibility issues, this process, in most cases, resulted in the replacement of multiple parts rather than the replacement of one desired section. The process was highly costly both in terms of money and time. Another disadvantage with this model was the poor residual value of the computer equipment. A system replacement often resulted in the invested capital being lost when the old system was replaced with a newer model.

In late 1993 Donald Becker and Thomas Sterling began sketching the outline of a commodity-based cluster system designed as a cost-effective alternative to large supercomputers [4]. The initial cluster computer consisted of 16 Intel 486 DX4 processors @ 100MHz, 16 MBytes RAM and 10 Mbit Ethernet Interconnects. The machine was an instant success. It was considered as an optimum solution without the many problems and disadvantages associated with the large mainframe and supercomputers.

Clusters can be built as result of interconnecting basic off-the-shelf computers, referred to as nodes. The main characteristics of a cluster are as follows:

- It consists of many of the same or similar type machines (heterogenous clusters are a subtype, still mostly experimental).

- It is tightly-coupled and uses dedicated interconnects.

- All machines share pre-specified resources such as a common memory segment.

- Initial software is required to setup the system for cluster computing.

The main advantages of clusters are that they are inexpensive and scalable. They are superior to supercomputers in terms of cost. Clusters need not be composed of the latest technology hardware available, and rarely need parts replacement. Their second advantageous factor, is evident scalability, when higher processing power is desired. Their performance may be improved by the addition of extra nodes rather than the replacement of parts. Scalability itself, however, is highly dependent on

the interconnect technology employed within the compute cluster [36]. The bandwidth and latency of the interconnect can determine the scalability of the hardware. Cluster architectures are physically more scalable than SMP<sup>1</sup> architectures. This is due to the increased aggregate interconnect bandwidth resulting from the addition of processors to clusters. In an SMP, the interconnect bandwidth remains constant.

The three main cluster application areas are as follows:

**High Performance Computing (HPC)** Executes programs with parallel algorithms.

**High Throughput Computing (HTC)** Used in parametric studies (same program executed many times with different parameters).

High Availability Computing (HAC) Provides fail-over redundancy.

Finally, cluster topology is a factor which users may use to their advantage. Clusters dependent on the employed interconnect can form various topologies, the most common of which is the *ring* formation. Although interconnects are considered one of the sources of performance loss within clusters, tuning of applications to a specific cluster topology may significantly minimise this loss of performance.

#### 2.2 Scalable Coherent Interface

A key decision that will greatly affect the overall performance of a compute cluster is the method used to connect the nodes together. Performance and scalability of traditional systems were limited by the scalability of the processor bus. Scalable Coherent Interface (SCI) was introduced to enable the extension of systems beyond the scalability limit imposed by the processor bus [12]. The scalable coherent interface (SCI) provides computer-bus-like services [26]. Unlike a bus, however, it uses a collection of fast point-to-point unidirectional links to provide the far higher

<sup>&</sup>lt;sup>1</sup>Symmetric Multi-Processor

throughput necessary for high-performance multiprocessor systems. SCI is a dedicated cluster interconnect, implemented according to the *IEEE Scalable Coherent Interface (SCI) standard 1596-1992*.

The most significant service offered by the SCI is the provision of a single physical 64-bit address space across SCI nodes and the related transactions for reading, writing, and locking memory locations in this hardware based distributed shared memory (DSM). SCI supports distributed shared memory with optional cache coherence for tightly coupled systems and message-passing for loosely coupled systems[19]. The employment of the unidirectional point-to-point links eliminates the dependency of bus length and bus speed on the size and number of processors on SCI topology. Point-to-point unidirectionality of the network also ensures lack of congestion within a simple ring based SCI network [21]. Distributed shared memory provided at hardware level within a compute cluster results in a low latency, high performance and deterministic behaviour of the technology.

"The Scalable Coherent Interface (Local Area MultiProcessor) is effectively a combination computer backplane bus, processor memory bus, I/O bus, high performance switch, packet switch, ring, mesh, local area network, optical network, parallel bus, serial bus, information sharing and information communication system that provides distributed directory based cache coherency for a global shared memory model and uses electrical or fiber optic point-to-point unidirectional cables of various widths." [5]

The scalable coherent interface as an "open" distributed bus also provides low-latency interconnections with full reliable communications for clusters [21]. High throughput, low latency and low CPU overhead are major factors which classify SCI as a high performance technology. Bandwidth and latency of SCI are sufficient in order *not* to impose any limitation on the performance and scalability of clusters. Meanwhile, the reliability of communication within SCI network, is also guaranteed through node-to-node request/response/acknowledge protocols, as well as the facilitation of split transactions (independency of the request and response signals) to prevent deadlocks. Address based communications, rather than stream based

methodology, result in the increased efficiency of SCI. Additionally, SCI protocols do not guarantee in-order delivery of transactions, hence the user must support this feature, through manual application, if desired.

One must appreciate that SCI is designed to serve both, message-based and shared-memory programming models [9]. Another feature of the SCI hardware, which will not be discussed in detail, is the ability to generate hardware interrupts on the remote nodes. This is performed by writing into the special status register address (mailbox) of the target node. Once the interrupt is triggered on the remote node, the SCI interrupt handler on the target node will be invoked and may perform the desired task or operation.

Exploiting SCI's flexibility in terms of its efficiency in supporting both parallel programming models - message passing and shared memory - leads to investigations targeting a distributed shared memory multiprocessor system similar to Stanford's FLASH [23], or MIT's Alewife [7] machines. The following subsection details how distributed shared memory (DSM) is achieved within a cluster through the use of SCI interconnects.

#### 2.2.1 Shared Memory using SCI

SCI, with its origin as a distributed multiprocessor bus, provides possibilities to directly access remote memory by ordinary load and store operations [37]. Since remote accesses are going through the I/O bus, these remote load/stores are often referred to as programmed I/O (PIO).

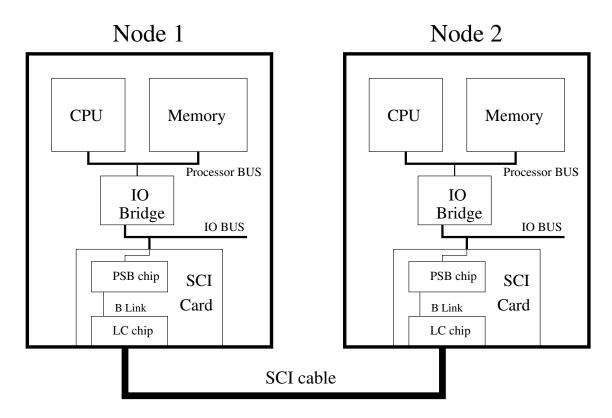

Figure 2.1 illustrates a typical architecture of an SCI based cluster. SCI technology has also accounted for caching of remote memory and thus target higher performances. Hence the resultant memory hierarchy is: (1) CPU registers, (2) CPU cache, (3) local memory or SCI cache, (4) remote memory [35]. Unfortunately this is not possible on PCI bus based systems, since transactions on the processor bus of a system are not visible by the (slower) PCI bus. Nowadays, PCI-SCI cards are used as cluster interconnects. PCI technology, in contrast to the motherboard technology, offers a unique interface for SCI cards, accounting for its employment in

Figure 2.1: Distributed Shared Memory diagram

a much wider range of systems.

As noted earlier, SCI protocols do not guarantee in-order delivery of transactions. This is a result of the transaction buffering capability on SCI cards. The bandwidth of the SCI network is greater than the normal PCI busses, hence it is not uncommon for the SCI transactions to be delayed as result of the delay within the PCI bus. In order to eliminate this issue SCI makes use of two concepts. The first is the split transaction mechanism, which also eliminates the possibility of dead-locks within the SCI network, while the second is the transaction buffering on the SCI card. Multiple stores to adjacent locations in remote memory can be gathered (by hardware) into internal buffers on the local PSB chip [37]. When a buffer is full, the PSB will transmit the contents of the buffer as a single, fully loaded SCI packet. Thus the overhead of SCI packet generation is amortised over many store operations. This technique is referred to as *streaming*. A read or store barrier operation may be used to flush all pending operations on the SCI network.

Each node can create shared memory segments in its I/O address space and export them into the SCI network. Other nodes import these DSM (Distributed Shared Memory) segments into their I/O space. A process may further map DSM segments into its virtual address space and from that point on, use standard load and store instructions to access shared, potentially remote memory. A processor can also send a lock operation (atomic read-write operation) to another node. SCI transactions are atomic and guaranteed to be delivered to the destination node.

They are assigned a unique id, which remote nodes use to import the segment. The remote node maps the exported memory segment (available through the SCI network) into its I/O address space, and creates an entry on its Address Translation Table (ATT). Additional options and configurations (known as segment flags and attributes) are also available to the user, which provide a series of services (such as security and access restrictions to the segment). Though potentially useful under some circumstances, they are undesirable in the context of this project, since they may introduce software interventions into the end system.

All remote operations are carried out by addressing part of the local address space, which is allocated for the SCI card on the PCI bus. Access to the local virtual memory is first mapped to a physical I/O address through the Memory Management Unit (MMU). The 32 bit PCI address is hence mapped into a 64 bit SCI address using the Address Translation Table (ATT) located on the board. The most significant 16 bits indicate the target node id, and hence also impose the restriction of maximum 64k nodes on any single SCI network. A portion of the PCI address is used as an offset to the remote memory segment and remains untouched. In most cases this is the 18 least significant bits. The remaining portion of the PCI address signifies the segment id. At the destination node, the least significant 32 bits of the SCI address are the physical I/O address on the target system.

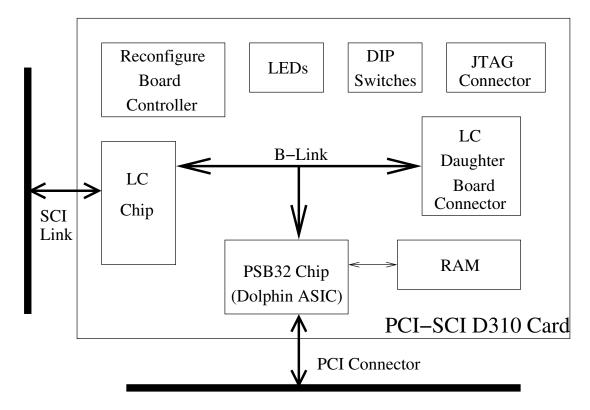

Figure 2.2 shows the basic overview of a PCI-SCI card. The B-Link operates as a backbone link between the PSB (PCI-SCI Bridge) and the LC (Link Controller) chips. The PSB (PCI-SCI Bridge) chip translates I/O bus transactions into SCI

Figure 2.2: PCI-SCI card overview

transactions (and vice versa), and this is the SCI interface to the local machine (PCI bus). The on-board ATT (Address Translation Table) stored within the RAM chip, is used to convert local I/O addresses into SCI addresses (and vice versa). The LC chip is the interface of the card to the external nodes. It manages data transfer on the SCI physical layer, as well as performing routing and delivery guarantees.

The board controller controls reset and initialisation of the board, as well as board status reporting and LED management. DIP switches are used to set various parameters on the card, such as the SCI link frequency, B-Link frequency and SCI window size. The daughter board connector supports an additional card for high fault tolerance and routing ability.

The PSB chip is a combination of the following components [15].

**PCI Interface** Interfaces the PCI bus and contains a DMA controller for high performance memory-to-memory transfer.

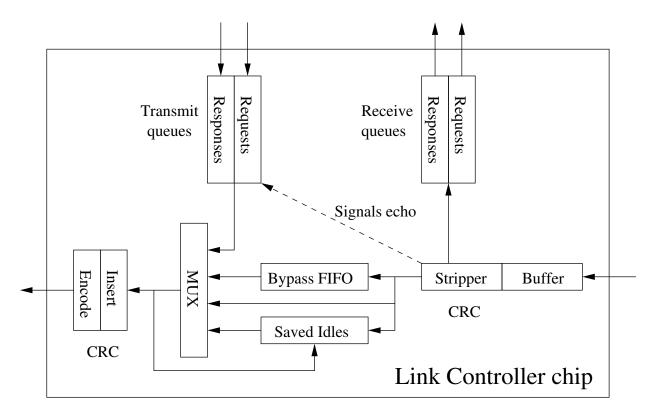

Figure 2.3: SCI Link Controller chip overview

**Read and Write Buffers** Read and write operation streams (16 streams with 128 bytes buffer each).

Address Translation Cache (ATC) Internal cache for mapping of 32 bit PCI addresses to 64 SCI addresses.

The PSB chip is formed by the top main components as well as a number of status and control registers for error logging, initialisation and status information.

The LC chip overview is illustrated in figure 2.3. Having already reviewed its role, the components present within the chip are briefly listed [15].

**Receive buffer** Input buffer composed of two queues, requests and responses. Packets are sent to B-Link from this buffer.

**Transmit buffer** Transmit buffer, again composed of two queues, requests and responses. Incoming packets from B-Link are placed within this buffer. In

some cases an "active buffer" is also present for retransmission in case of an error. Packets are discarded on receipt of a correct echo.

**Bypass FIFO** Stripped incoming packets, if not destined for this node, are placed within this queue for transmission to the next node.

**Saved Idles** These are SCI packets, inserted in between SCI packets for permanent synchronisation of the chip to the incoming data.

# Chapter 3

### REAL-TIME OPERATING SYSTEMS

Real-time operating systems are an important class of operating systems. An operating system is considered to be "real-time" if it possesses a strict set of policies and rules regarding its execution, the most important factor being the timing constraints [18]. Kernels designed for such operating systems are required to be extremely efficient, highly deterministic and to perform execution within a specified timing constraint.

If we model an operating system as a simple process, which takes a set of inputs and outputs a set of results after internal computations, then a real-time operating system is one which, is expected not only to produce a correct set of results, but also to output results within a finite timing duration from the moment of presentation of inputs to the system.

The strict timing issue of an operating system further implies that the operating system must perform tasks on a deterministic and highly efficient basis. The following is a fundamental description of a real-time operating system from the early 1980s.

"[An environment] characterised by processing activity triggered by randomly accepted external events. The processing activity for a particular event is accomplished by sequence of processing tasks, each of which must complete within rigid time constraints. ...Characteristically, the computer system is completely dedicated to the control application and has been configured to guarantee on-time responses even at peak loads. The environment is such that utilisation of equipment is less important than responsiveness to the environment." [18]

Often a very strict hierarchy of commands is built-in to the real-time operating

systems. This is to allow for a certain level of flexibility for programmers while driving the fastest response possible from the real-time hardware. In recent years a set of rules and policies have been outlined which must be met by developers to achieve a real-time operating system. Some of these rules & policies are outlined below [22] [24]:

- A RTOS<sup>1</sup> should be a multitasking design in order to maximise the CPU's efficiency.

- The kernel should be driven in response to internal and external system events.

- The kernel should support a number of independent or interrelated tasks, each having its own priority associated with its scheduling importance.

- The kernel's performance should be highly deterministic.

- The kernel should be designed so as to impose minimal overhead to the application tasks and should have small RAM requirements.

- Common rules of task scheduling apply (higher priority task preempt lower priority tasks and the Null task always has the lowest priority).

- The kernel must be interruptible but not re-entrant.

- An interrupt service routine (ISR) must not issue kernel system calls except to signal another event or to terminate itself.

Real-time operating systems are rarely implemented fully in software. Hardware in most cases is custom designed with the intention of providing real-time capabilities. Hence, low level debugging tools such as simple background debuggers, logic analysers and emulators are used to address flaws within the system.

<sup>&</sup>lt;sup>1</sup>Real-Time Operating System

Applications of real-time systems are growing and will continue to do so. Many applications require real-time systems to deliver their objectives with timing constraints, from the simplest systems such as a watch to the most sophisticated systems like NASA space shuttles. They are classified into two types, based on their timing constraints. These types are called "hard real-time" systems and "soft real-time" systems. Each type will be addressed individually, and some general common issues and services involved within the kernels of such systems will also be discussed.

# 3.1 Hard Real-Time Systems

Hard real-time systems guarantee completion of a critical task within the specified amount of time. To achieve this, all delays within the system must be bounded and all operations must take a deterministic amount of time to complete. The scheduler plays an important role in hard real-time systems. Generally a process/task is submitted to the scheduler along with the time necessary to complete its operation. The scheduler will then either accept the process/task or reject it.

The scheduler will accept the task if it can guarantee the completion of the job within the specified amount of time. It will reject the task if it considers it as impossible to complete within the provided time limit. For the scheduler to be able to make such a judgement accurately, it must know the exact execution time length of each operation within the system.

Hard real-time systems are hence restricted as to what devices or operations they can support. Secondary storage devices and advanced operating system features are two major areas which are mostly absent in hard real-time systems due to the uncertainty involved in their response.

Examples of where hard real-time systems are used are NASA space shuttle systems, FAA (Federal Aviation Administration) systems, critical medical equipments, weapon & military systems and some automobile-engine fuel-injection systems. They all require objectives to be met within a specific time-line and failure to do so will be regarded as complete failure of the system.

#### 3.2 Soft Real-Time Systems

Soft real-time systems are less restrictive than hard real-time systems. Tasks and objectives within such systems are allowed to be completed within a bounded period. The scheduler in such systems must be priority based. It must assign the highest possible priority to the real-time jobs, and ensure that their priority does not degrade over time. Non-real-time jobs are allocated variable priorities, and their priorities are allowed to vary throughout execution time.

The scheduler must at first level satisfy the real-time job requirements, and at second level handle non-real-time jobs. Although the scheduler is allowed to act more freely regarding non-real-time jobs, it should not allow long delays, starvation or unfair resource allocation among such jobs. This in most cases makes the design of the scheduler an extreme challenge, because the scheduler is expected to schedule jobs such that it completes all tasks with the minimum overall delay possible. In particular, dispatch latencies are minimised as much as possible (using efficient designs) so as to allow the execution of real-time as soon as they are executable.

Applications of such systems are extremely broad since unlike hard real-time systems, they can support various devices and operating system features. Thus they are used in many multi-media, graphics, virtual reality and advanced scientific systems and will continue to grow rapidly over the coming years.

#### 3.3 Real-Time Kernels

Real-time operating system kernels as mentioned are very limited on the operations that they may perform. It is aimed that all supported operations within a kernel be deterministic and efficient. This has resulted in most RTOS's in today's market offering a similar set of services, which will be outlined here.

Kernels must manage system resources efficiently. The main system resources are the CPU, memory and time. The CPU is shared to increase efficiency and execute processes faster. Memory management is an issue because it is a finite resource. Time, as mentioned earlier, is the most important factor that every real-time system should manage in order to deliver its objectives.

Considering that the use of real-time systems is mainly within embedded devices, which might impose size, power consumption, memory and other restrictions, having the kernel as small as possible is desirable [41]. The user may add further tasks if required, but these are at the expense of cost of a larger system, possibly slower performance and the variation of other parameters.

Schedulers, as discussed, are the most significant part of the kernel. There are three main types of schedulers which most real-time kernels use [22]:

- Round robin scheduling

- Time sliced scheduling

- Preemptive scheduling

Preemptive scheduling is the most popular, supporting the other two scheduling methods. It uses priorities along with event driven operation.

Services among kernels are more variable. In advanced kernels, the user must specifically request certain services at compile time if he/she wishes to use them within the application. Otherwise the kernel would not include such services, resulting in a reduced size and faster operation of the kernel. Some services, however, are critical and are present within all the systems. A short list of common kernel services are outlined below [22].

- Static and dynamic task services

- Queues and lists

- Semaphores

- Mailboxes

- Synchronous and asynchronous transmission

- Timers

# • Memory management

Finally we present a list of properties which industrial users commonly use to compare and evaluate RTOS's for their applications [28].

- The interrupt latency (i.e. time from interrupt to task run).

- Maximum time period for execution of every single system call.

- $\bullet$  The maximum time the  $\mathrm{OS}^2$  and drivers mask interrupts.

- System interrupt levels.

- Device driver IRQ<sup>3</sup> levels.

The above parameters are fixed regardless of the application program. Users possess the knowledge that systems operate in a deterministic fashion and estimate whether their hard real-time jobs can complete on such systems or not. They choose the hardware together with the RTOS such that it meets their objectives with minimal cost.

<sup>&</sup>lt;sup>2</sup>Operating System

<sup>&</sup>lt;sup>3</sup>Interrupt ReQuest

# Chapter 4

## SCI DRIVERS

Device drivers are the most essential part of resource management within a system. In this context, resource refers to a hardware device which the user uses to obtain its objectives. SCI drivers play an important role in allowing systems to make correct, efficient and organised use of SCI hardware devices.

SCI provides high speed communication (an interconnection) between cluster nodes. It is "the" element, which allows independent, separated nodes to engage in cluster computing and processing of collaborative tasks. Hence examination of SCI drivers is extremely important in order to achieve a cluster with a performance comparable to those of supercomputers.

SCI drivers, as a portion of the real-time system, must obey all restrictions imposed on the system. Therefore, the real-time issues must also be examined and satisfied within the device drivers.

We shall start this chapter with a brief look at device drivers in general. Having identified the roles and objectives of a device driver, we will discuss the operation and implementation of device drivers on two of the most important operating systems (on which SCI drivers have already been implemented). The next section examines the general structure and arrangement of SCI source code drivers. Compilation, building, configuration and loading of SCI drivers are outlined in the following section. Finally, two major parts of the SCI drivers are discussed individually with a detailed analysis of their tasks, roles, initialisation sequences, resource requirements and inter-communications.

#### 4.1 Drivers

A driver supplies a uniform, device-independent, logical interface which allows the user to interact with a device. They contain detailed knowledge of hardware devices and ensure correct and proper use of the device by the system and its users.

While they provide the mechanism of accessing hardware functionalities, they should not provide any policy regarding the use of such services. In other words, the drivers simplify the use of hardware functions, but may not impose any additional restrictions for doing so.

Device drivers are particularly important in providing compatibility between systems and a range of developed hardware devices. Along with the drift of technology, hardware becomes more advanced and offers new features and functionalities. Drivers must ensure that a *unified* interface is provided regardless of the version/model of a device. It is the drivers' responsibility to provide various implementations of their interface in order to support all models of a hardware device.

Device driver implementations vary among operating systems. Each operating system kernel has its own set of policies regarding loading, initialisation, configuration and access to resources within the system. This enforces various implementations of device drivers for different operating systems. We will examine policies and rules imposed by Linux and VxWorks operating systems, and later demonstrate how this is achieved within SCI source code drivers.

#### 4.2 Drivers on Linux

Device drivers on Linux operating system are classified into two types based on their position in the system. The first class are the built-in device drivers. This set is compiled and linked into the kernel at the kernel build stage. Built-in drivers have the disadvantages of increasing kernel size and introducing additional overhead to the system. However, they provide better reliability, performance, security and speed due to being part of the system core (the kernel). Drivers are built-in to the kernel if (i) They are in constant use, (ii) A high operational speed is desired or (iii) If security is a significant issue [8].

Built-in drivers initialise as part of the kernel initialisation process at system startup [13]. They do not generally terminate until the system shuts down, but privileged users may terminate some built-in drivers partially at run-time.

The second class of device drivers are known as *modules*. These are much more popular and more common within the system. Built-in drivers, as mentioned, are only reasonable if used on a very frequent basis. However, this is rarely the case and thus modules were introduced. Modules are, in a general sense, a set of kernel functionalities which are loaded into the system whenever an application or user desires their functionalities.

They have three distinct features which separate them from any other normal program. Once these three basic rules are met, any program can fall into the module category.

- 1. It must provide an initialisation routine (init\_module function).

- 2. It must provide a cleanup routine (cleanup\_module function).

- 3. It must either define, or be compiled with a relevant set of definition flags, indicating that it is a module, and it should be executed within the kernel space.

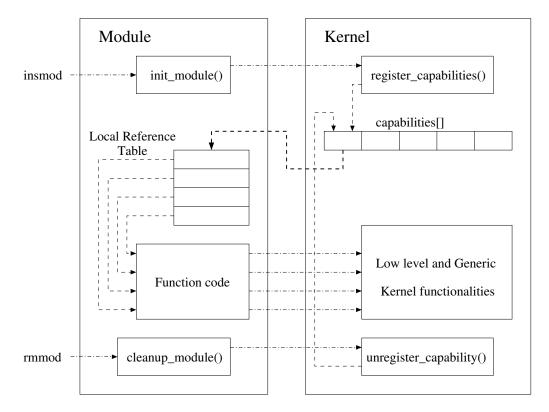

The init\_module¹ function is the first function which is called when a module is loaded into the Linux kernel. It is responsible for allocating the necessary resources, tables and registration of its symbols into the kernel public symbol table. The kernel symbol table can be read in text form from the file /proc/ksyms. The table holds a list of functions which are supported by the kernel. In fact in most cases, the init\_module makes use of such functions to allocate resources to the driver. The init\_module calls the kernel register\_capability function to register its capabilities. The kernel inserts the module capabilities within the system capabilities [] array, which indirectly references the start of function routines.

$<sup>^1</sup>$ the user may specify an alternative initialisation routine using the  ${\tt module\_init}$ () function at the start of module code

Figure 4.1: Linux Module-Kernel Inter-communications Diagram

Conversely the cleanup\_module<sup>2</sup> function unregisters the capabilities from the kernel capabilities[] array and releases all held resources.

Figure 4.1 illustrates the basic relationship between kernel and module as explained. The insmod and rmmod functions may be used by privileged users to enforce module loading and unloading. A list of loaded modules can always be examined through /proc/modules. I/O region allocations can also be examined through /proc/iomem and /proc/ioports files.

Linux drivers are further classified into three types, and since they are mostly implemented as modules, they are termed *char modules*, *block modules* and *network modules*.

Character devices Similar to normal files, these devices are accessed as a stream of bytes. The driver implements basic open, close, read and write system

<sup>&</sup>lt;sup>2</sup>the user may specify an alternative cleanup routine using the module\_exit() function at the start of module code

calls. This data channel may only be accessed sequentially.

Block devices These devices are very similar to character devices. Data is usually accessed (read/write) in multiple blocks<sup>3</sup>. The only difference compared to character devices is the way in which data is handled internally by kernel.

**Network interfaces** These are hardware or software <sup>4</sup> devices which exchange data with other hosts. They transmit and receive data packets. The kernel also makes packet transmission based calls rather than reads and writes.

Every hardware device within the Linux system has a major and minor number associated with it. The major number indicates the class of the hardware, whereas the minor number is an index into the device <sup>5</sup>. Drivers initially find their devices on the system using the major number. Having found the device on the system<sup>6</sup>, they can interact with the target device through kernel system calls. Often for optimisation and efficiency reasons, such system calls are defined as macros which reference lower level codings<sup>7</sup>.

#### 4.3 Drivers on VxWorks

VxWorks is a commercial real-time operating system. It is widely used in industrial systems and has substantial support for a wide range of devices. However it is considered somewhat unsuitable for research and academic environments. In response to the "What is a good RTOS?" question, developers and users on the Comp.realtime newsgroup jointly agree on the following answer, which is presented in the FAQ section of the news group.

"A good RTOS is not only a good Kernel! A good RTOS should have a good documentation, should be delivered with good tools to develop and

<sup>&</sup>lt;sup>3</sup>each block is usually one kilobyte

<sup>&</sup>lt;sup>4</sup>such as loopback interface

<sup>&</sup>lt;sup>5</sup> often zero, unless several devices of same type are present (e.g. multiple network cards)

$<sup>^6{</sup>m this}$  generally implies knowing the bus and pci device numbers

<sup>&</sup>lt;sup>7</sup>in most cases, Assembly language code

tune your application. So even if some figures like the Interrupt latency, Context switch time are important, there are a lot of other parameters that will make a good RTOS. For example a RTOS supporting many devices will have more advantages than a simple very good nano-kernel." [6]

The lack of any proper documentation, information or source code of VxWorks internals are the main factors which prevent it being addressed in any research or academic program. Conversely, supporting a wide range of hardware devices, a significant amount of usage and interface documentation, along with extensive results on testing and evaluations have made it one of the most popular real-time operating systems in the industrial world.

It must be noted that substantial efforts were made in the study of VxWorks internals with regard to device driver implementations. The information provided here is comprehensive but by no means complete. While no reliable documents<sup>8</sup> were found to verify the following concepts, we believe, to the best of our knowledge, that they are accurate and correct.

A short overview of the system will be presented, followed by an outline of the driver implementations of the two most important device types on VxWorks.

VxWorks provides a real-time kernel that interleaves the execution of multiple tasks by employing a scheduling algorithm. Thus the user sees multiple tasks executing simultaneously. VxWorks uses a single common address space for all tasks, thus avoiding virtual-to-physical memory mapping. Complete virtual memory support is, however, available with the optional vxMem library.

A task is an independent program with its own thread of execution and execution context. Every task contains a structure called the task control block which is responsible for managing the tasks' context. A task has four states as outlined below:

**Ready** Task is ready to be scheduled for execution.

**Delay** Task is put to sleep.

<sup>8</sup>this section is mainly based on "VxWorks - Device drivers in a nut shell", AyyalaSoft.

Suspend Task has been initialised, but not activated yet

or is debugged

or interrupted by an exception.

**Pend** Task is waiting for a resource.

The VxWorks scheduler runs a preemptive algorithm, which guarantees that the highest priority task preempts a lower priority task.

"Interrupt" is the mechanism by which a device seeks the attention of the CPU. The code which handles such interrupts is called interrupt service routine (ISR) or interrupt handler. Interrupt response time is the period starting from the occurrence of the interrupt to execution of the first ISR instruction. This period is composed of interrupt latency, delay for saving the task context and execution of kernel ISR entry function.

VxWorks provides a special context for interrupt service code to avoid task context switching, and thus renders faster responses. VxWorks supplies interrupt routines which connect to C functions and pass arguments to the functions to be executed at interrupt level [42].

All interactions with hardware devices in VxWorks are performed through the IOsub-system. VxWorks treats all devices as files. The two most important devices are *character devices* and *block devices*. There are two points which are common across both types of device drivers [42].

- Drivers in VxWorks can be dynamically loaded and unloaded.

- Drivers work in the context of the task invoked by an interface routine. Hence drivers are preemptable and should be designed as such.

There are four major issues involved in implementation of a Character device driver on VxWorks.

Driver installation The iosDrvInstall() and intConnect() directives are used

to provide basic driver functionality references<sup>9</sup> and activate the hardware device related ISR, respectively.

Device descriptor registration The iosDevAdd() is used to add the device to the I/O system device list<sup>10</sup>.

Support for interface definitions Developer should provide code for all referenced driver functions<sup>11</sup>.

**Support for interrupt handler**<sup>12</sup> Developer should provides device ISR, which is called when CPU receives an interrupt from target hardware.

Block devices interact with I/O systems through file-systems. Each block device is associated with a file-system. Block device drivers provide logical device structures. Logical device structures describe the device and contain routines to access the device in a general fashion via the underlying file system. Furthermore, it is the file system and not the block device driver which is installed as an entry into the I/O system driver table. The steps which define the development of block device drivers are as follows:

- Define and initialise all interfaces within the logical device structure;

- Associate and register the corresponding file system for the block device;

- Setup and connect the ISR.

Section 5.6 details device driver implementations on RTEMS, prior to a comparison of device drivers implementations on all three systems in Section 5.7.

<sup>&</sup>lt;sup>9</sup>the user must provide function references for the *create*, *remove*, *open*, *close*, *read*, *write* and *ioctl* driver functions

<sup>&</sup>lt;sup>10</sup>users can execute driver function calls through the I/O system device function table

<sup>&</sup>lt;sup>11</sup>the most important function is the IOCTL since users control the device through this function

#### 4.4 Structure of SCI Drivers

The examination and study of SCI drivers have certainly been of crucial importance throughout this project. SCI drivers are by far one of the largest and most complex set of drivers seen for a PCI card. On Linux platform, the SCI set of drivers is at least twice as large as SCSI drivers<sup>13</sup>.

Throughout the introductory chapters, it was emphasised that all SCI protocols are carried out at hardware level, resulting in a low latency and high performance technology. One may wonder why SCI drivers (software) are of such importance? The reason is the tight connection of SCI and systems memory management in the nodes. Together with the requirement of connecting operating system kernels that have no knowledge of their counterparts on the other nodes, this makes SCI drivers rather complicated and probably the most complex of all drivers.

Unfortunately, lack of documentation, and the existence of few informative files within the driver source code forced us to thoroughly examine 37MB of source code! The information obtained is believed to be valuable and as stated within the Introduction Chapter, a simplified internal view of SCI drivers is presented in the hope that the information provided here will be useful for all future developers, who plan to examine, study, use, develop and extend the SCI technology and corresponding drivers.

The SCI drivers may be broken into two sections at the root. One section, labelled adm, allows users to compile, build drivers and conduct tests without the intervention of source codes and knowledge of SCI internals. Various scripts have been provided within the bin directory (located within adm directory) for each supported operating system to allow the user to compile, build and install drivers for different sets of cards.

The alternative to *adm* is *src*, which enters into the source code tree of SCI drivers. The SCI driver is split into two main parts.

$<sup>^{13}</sup>$ by many known to be the largest Linux device driver shipped with Linux distributions

Figure 4.2: IRM Internal Structure

IRM IRM<sup>14</sup> is a low level driver which interacts directly with the SCI hardware. It also provides higher level interfaces for low level programs, higher level drivers and modules such as SISCI, for reliable and simplified access to SCI resources.

SISCI SISCI is a higher level driver providing resource management and a simplified access interface for user level applications to the SCI adapter. While SISCI is a higher level driver relative to IRM, it is still considered as a low level driver and many additional layers are coded within the industry to sit on top of it for further simplified user interface.

Figure 4.2 illustrates the internals of the IRM and its interfaces. Three interfaces and one component directly interact with the *IRM Core*. The most significant interface is *genif.h* which provides full interface to all external resources. The *IRM Utilities* are a series of tools which allow users to configure the SCI adapter card. The

<sup>&</sup>lt;sup>14</sup>Interconnect Resource Manager

test and demo programs are both a set of applications designed for testing and simple operations using IRM device drivers. Finally, while all external sections of IRM partially interact with the core directly, most communication is directed through an internal *sciLib.h* interface facilitated also by the *IRM Internal Library* section. All external resources and higher level drivers (such as SISCI) **must** communicate with IRM through a general interface<sup>15</sup>.

# 4.5 Compilation, Build & Configuration

This section very briefly describes the procedure required to perform *custom* compilation, build and configuration of the SCI drivers. Of course, a set of scripts is already available within the root *adm* directory which simplifies all of this for the user.

There exists a build script within the IRM directory, which compiles and builds the IRM driver. The user must supply its operating system, architecture and adapter type in order for this script to compile the corresponding set of drivers. The result in most cases, is a binary object file, labelled *pcisci.o.* In the case of Linux operating system this would be the IRM module, which as indicated in previous sections, can be loaded into the system.

Similarly the SISCI directory contains a build script which provides a second binary file, labelled *sisci.o.* This script also requires the operating system and adapter type to compile the relevant set of source codes.

The compilation of both sets of drivers is done using GNU Makefile utilities. SCI drivers use Makefiles in conjuction with some shell scripts to compile the relevant source codes. The makefiles relevant to IRM, are not only scattered through the source directories, but an exclusive set is also present within the drv/src/MAKE directory. SISCI driver makefiles do not have a particular location and they are mostly scattered through the SCI driver structure.

SCI drivers seem to use run-time shell scripting as a hack to GNU Makefile procedures to achieve a finer control over the compilation of the drivers. Relevant

$<sup>^{15}</sup>$  qenif.h

shell scripts are produced <sup>16</sup> and executed at the runtime stage of GNU Makefile utilities. This not only results in a high level of complexity in the compilation and build process, but it also increases the complexity of transferring such drivers to other platforms.

GNU Makfile utilities, nowadays, offer excellent flexibility and configurability[14]. We shall see how our target operating system (RTEMS) has used the latest of such tools to achieve a robust set of Makefiles within their source code structure.

The configuration of the adapter is considered when loading the driver into the system. The generated pcisci.conf specifies the configuration files to be used for configuring the irm,  $psb^{17}$  and  $lc^{18}$  sections. Only experts are recommended to specify their own configuration files, and in most cases it is recommended that irmConfig.h be used. This file contains default configuration for all sections of the board.

#### 4.6 IRM

Interconnect Resource Manager is the lowest level of SCI driver code, which interacts directly with the SCI adapter. The source code supports a wide range of operating systems with all commercially available SCI cards. The present set of available SCI cards are:

- PCI1 (PSB32) adapter;

- PSB64 adapter;

- PSB66 adapter;

- SBUS2 adapter.

$<sup>^{16}</sup>$ mostly through drv/src/MAKE/mklib.sh

<sup>&</sup>lt;sup>17</sup>pci-sci bridge

<sup>&</sup>lt;sup>18</sup>link controller

Figure 4.3: IRM source code structure

A general overview of the IRM source code is shown in Figure 4.3. On the left hand side and at the bottom of this figure, a series of operating systems which the SCI drivers support are shown. The ones of major importance are Linux and VxWorks as these will be examined in-depth in the Implementation Chapter. On the right hand side of the diagram, a list of all supported SCI card models is shown.

Depending on the set of options passed at compile time, the makefiles select the relevant sections and compile, build and merge them together for the final binary IRM driver object file.

Firstly, the interaction of the three sections <sup>19</sup> within the IRM source code will be examined.

The adapter dependent code itself splits into three sections. The first part is the *Link Controller* section. This controls the link controller chip on the SCI card. Several header files in this directory provide various structures which contain the

$<sup>^{19}</sup>$ IRM core source code, operating system dependent and adapter dependent code

location, type and significance of each register controlling the link controller chip. The second part relates to the PCI-SCI Bridge chip, known as the psb section. Similar to the link controller section, this section also provides informative structures regarding the registers on the PSB chip. The last section is the general adapter code which provides all the adapter specific functionalities listed in the drv/src/adapter.h file. This final section uses the structures provided from the previous two sections to read/write and configure the chips located on the SCI card. Hence, in an overview of this paragraph the adapter dependent section provides the adapter specific functionalities outlined in the drv/src/adapter.h file.

The operating system dependent code is the main interface through which the IRM driver interacts with the target operating system. This section is somewhat complicated due to the tight connection of the SCI drivers with the memory management of the operating systems. There are three main interfaces which the IRM driver requires to be supported by the operating system section. The first is comprised of various operating system related functionalities and is detailed within the drv/src/osif.h file. This section facilitates access to hardware, low level resource (data and register structures which reference on-chip registers) allocation and management, handling of events and interrupts, as well as locking, synchronisation and mutual exclusion which are required throughout the SCI drivers. The second is related to memory management and lists the desired functionalities within the drv/src/memalloc.h file. Tight connection of the SCI technology with memory management of operating systems requires support of a significant number of memory related functionalities, such as I/O buffer space allocation, memory locking (makes memory non-swappable), memory alignment (ensures the starting address of memory chunk is divisible by a certain alignment parameter), contiguous memory allocation, DMA transfer and many other functionalities. The last section is the SCI driver initialisation routine, which each operating system section must provide.

The section from the IRM core which relates to the initialisation routine is the bootstrap section. The file drv/src/ldbootstrap.c is used to indicate the approach taken for initialisation of IRM driver within the target operating system.

```

#if defined(Linux) || defined(OS_IS_VXWORKS)

extern ROUTINE init_module;

#ifdef OS_IS_VXWORKS

extern ROUTINE sci_get_local_csr;

#endif

static ROUTINE *syscall_required[] = {

init_module,

#ifdef OS_IS_VXWORKS

sci_get_local_csr,

#endif

};

#else

```

According to the above code<sup>20</sup>, both Linux and VxWorks would like to initiate the driver by calling the init\_module function, but VxWorks also proceeds with the sci\_get\_local\_csr thereafter.

The IRM core section contains numerous interfaces and source files to perform various operations. The most important interface provided by the IRM core, as previously mentioned, is the drv/src/genif.h interface, which interfaces all allowable functionalities through the driver and should be used by all higher level code, driver and applications.

The IRM core consists of 2.1MB of source code, which supports all SCI technology related functionalities that are operating system independent, but not necessarily adapter independent. These functionalities include Session management, support for SCI communication protocol, Virtual Channel management, Mailbox and Interrupt management, Address Translation Table (ATT) configuration, adapter management, PCI and B-Link bus control, DMA engine support, Link Controller chip management, remote memory operations library, Switch, Timer, Topology support along with many other functionalities. The final IRM issue to be discussed is the initialisation routine, which must be implemented by the operating system dependent

$<sup>^{20}</sup>$ taken from the drv/src/ldbootstrap.c file

section, and is thus investigated more thoroughly in following subsection.

## 4.6.1 IRM Initialisation

The SCI card initialisation routine is of substantial importance within the IRM drivers. Most functionalities of the card are performed at hardware level, which implies that the initialisation process holds greater responsibility in initialisation and configuration of the card. This is to allow for hardware based operation of the card at a later stage.

The initialisation routine is comprised of both operating system [OS] dependent and independent code. The OS dependent section mainly facilitates access to the card and registers within the card, as well as resource allocation and management in the system. The OS independent section configures and initiates the card and resources using the OS dependent layer and this section is primarily dependent on the card model.

Although we are only interested in the OS dependent section of the initialisation routine, one must stress that the OS independent section was also studied in-depth to ensure correct functionality and elimination of unnecessary code under the target operating system. Lack of documentation of this routine was another reason which supported the idea of representing the initialisation routine through a sequential process. Finally, every effort has been made to eliminate the complex nature and inter-communications of the routine, but where necessary sufficient detail has been provided to fully explain the objective.

PCI-SCI D310 Initialisation routine:

Find the PCI-SCI card Initialises the PCI BIOS interface and searches through the PCI bus for any device matching SCI card vendor and device tags.

Adapter Table creation Allocates memory to hold the adapter table information.

Adapter Table initialisation Places preliminary information obtained about the PCI device into the adapter table.

**Setup PSB memory areas** Sets up the memory descriptor for the PSB's csr, IO and prefetch space.

Store interrupt line Obtains the interrupt line number from the card memory.

Map PSB memory areas Maps the PSB's csr, IO and prefetch space into kernel memory.

Check PSB Verifies that the PSB is present and alive.

**Lock creations** Creates semaphore locks for Main\_Driver, DMA, FlagIntr, ATTindex and timeQ.

Initiate the timeout job handler Initialises a separate thread which creates a message queue awaiting jobs to be dispatched from the timer thread to be executed <sup>21</sup>.

**Pre session and VC initialisations** Preliminary configuration, resource allocation prior to attachment of any adapter.

**Attach SCI interrupt** Attaches SCI interrupt handler to the ISTAT register of the card <sup>22</sup>.

**PSB** chip verification Reads and ensures that the PSB chip ID and revision match the ID and revision of the the current set of drivers <sup>23</sup>.

**Obtain config info** Obtains configuration info related to the card either from the adapter non-volatile memory or the config struct that has been previously filled in by a config operation.

<sup>&</sup>lt;sup>21</sup>the general\_timeout\_handler is called which removes the job from jobs list and subsequently executes it

$<sup>^{22}</sup>$ the handler reads and executes the jobs specified at the ISTAT register of the card

$<sup>^{23}</sup>$ in our case the chip ID is 0x3D65806D signifying PSB32 and rev D

**Insertion of config info** Places the obtained config info into the SCI adapter structure.

**Setup physical ID table** Dependent on LC and PSB chip model, initialises the physical topology settings on the LC chip.

Configure LC chip Initialises and configures the LC chip related registers.

Initialise interrupt mask Stores the interrupt signal masks and their significance.

Set GX timeout Sets up the (possible) GX hostbridge to 30ms timeout on PCI.

**Set NX** In the case of the PCI host bridge type being HB\_450NX\_PXB, turn on the BWCE<sup>24</sup> and turn off the Assert SERR# on the inbound delayed read time-out.

Set ServerWorks Latency In the case of the PCI host bridge type being

HB\_SERVERWORKS\_LE, set PCI Latency Timer to ensure enough time for

PCI burst transfer.

Enable write posting Enables write posting on PCI host bridge.

**Pre PSB initialisation** Sets up BIU Control, SlDeadlkCnt, Misc Control registers, CSR access protection, interrupter, windows protection and Stream configuration in PSB and initialises PCI CSR.

Misc operations A mixture of random configuration reads and sets (related to both PSB and LC chips), plus the enabling of numerous board related functionalities (such as StoreBarrier, ATT initialise, nodeProbe, Client ErrCheck and Software packet buffer allocation).

${

m VC}$  initialisation Starts the  ${

m VC}^{25}$  watchdog and module for the adapter.

<sup>&</sup>lt;sup>24</sup>Burst Write Combining Enable

<sup>&</sup>lt;sup>25</sup>related to recieve and transmission functionalities of the card

**DMA** initialisation Starts the DMA engine<sup>26</sup> on the board.

**Switch module configuration** The Card predicts and sets the switch ID to which it belongs on the overall SCI topology.

Interrupt info initialisation Initialises the interrupt counters monitoring the jobs and tasks performed by order of the ISTAT register.

**PSB** initialisation Sets up final configuration of the PSB chip and starts the chip<sup>27</sup>.

Final watchdog activations Starts the LC chip and session watchdog<sup>28</sup>.

At the end of this routine the software intervention of the driver initialisation is over, but the hardware still performs necessary initialisations through a set of timer functions which it deems necessary. The osif\_timeout is the function which is called with time related jobs. It creates watchdogs for each job which expire at the time chosen by the caller. Once a watchdog expires it submits the job into the jobs message queue, which is subsequently handled by the timeout job handler for execution. The majority of jobs are created through the hardware calls, ISTAT register and interrupt handler routine.

#### 4.7 SISCI

SISCI is a higher level driver for enhanced resource management and simplified programming interface for user applications [16]. It maintains a table of resources held by user applications, and in the case of failure of the application task, it manages the resources and releases them appropriately. The SISCI is also responsible for bridging the user mode operations into kernel mode operations, allowing user applications, which are normally in the user space, to access IRM functionalities at kernel

<sup>&</sup>lt;sup>26</sup>enables for DMA transfer between nodes

<sup>&</sup>lt;sup>27</sup>resulting in full functionality of the chip on the PCI bus

<sup>&</sup>lt;sup>28</sup>bringing the card to a state where it can interact with external nodes as well

Figure 4.4: SISCI source code structure

or privileged user space [16]. Requests, addresses and data from the user space is copied and/or converted to the kernel execution space. Data in most cases, is simply copied from users space to the kernel space. Requests are converted/decoded into a series of IRM commands and functionalities, which are performed to deliver the objective. Addresses are also converted from the user mode to the kernel mode, referencing the coped data from the user space to the kernel space.

Figure 4.4 shows how IRM, SISCI and user applications interact with each other. As shown, the SISCI driver is mainly split into two sections, the Core and the  $API^{29}$ .

After compilation of the SISCI driver, the user is presented with a binary *sisci.o* file. In case of Linux, this is yet another module which has to be loaded into the kernel. This module contains the core section of the driver, which as shown in the diagram, interacts with IRM through the *genif.h* interface. The second section of

<sup>&</sup>lt;sup>29</sup>Application Programming Interface